#### **MIPS Datapath**

CMSC 301 Prof Szajda

- Build an architecture to support the following instructions

- Arithmetic: add, sub, addi, slt

- Memory references: lw, sw

- Branches: j, beq

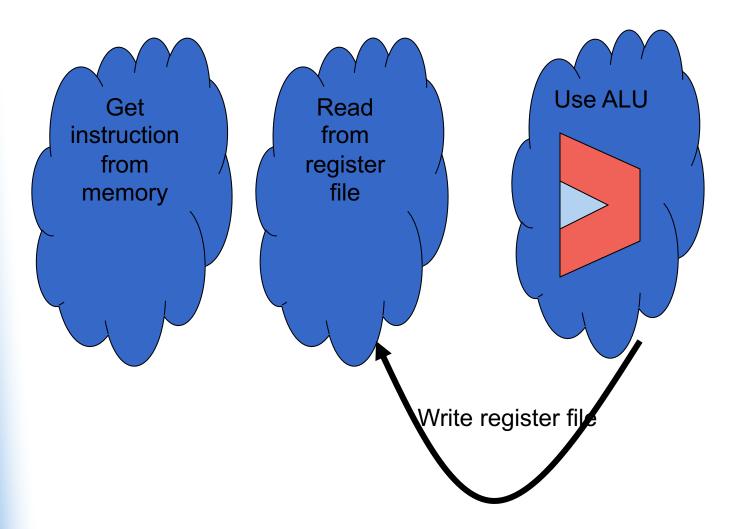

#### Process

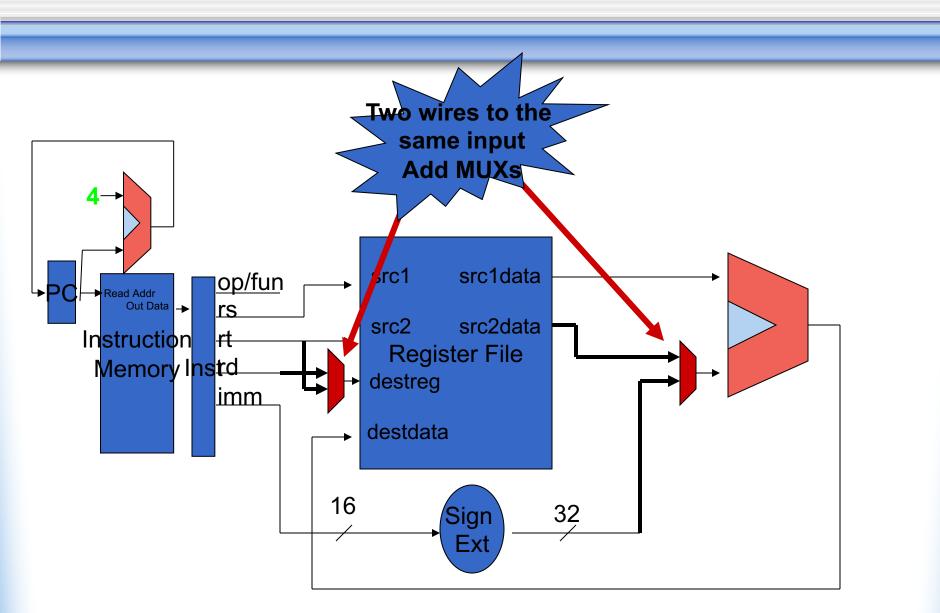

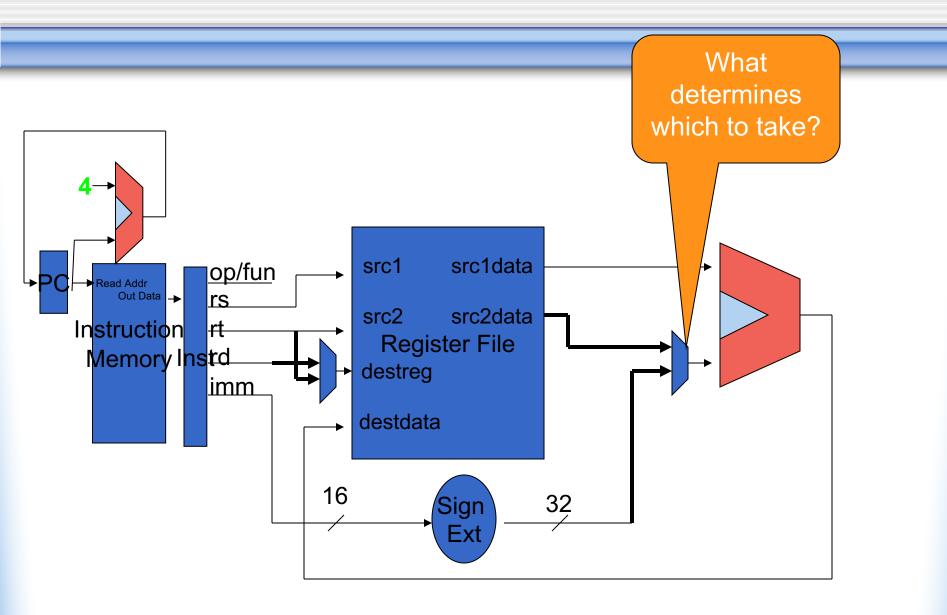

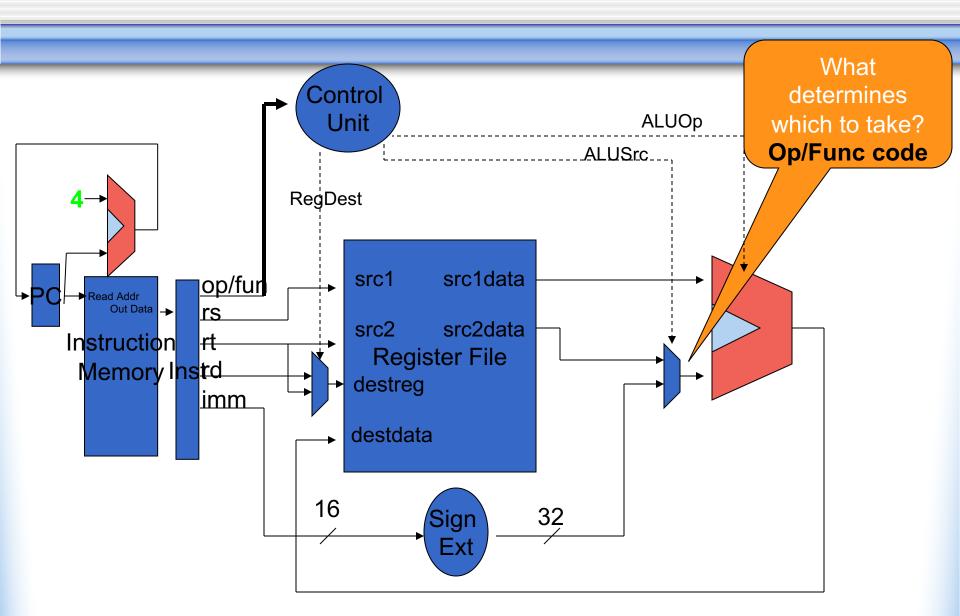

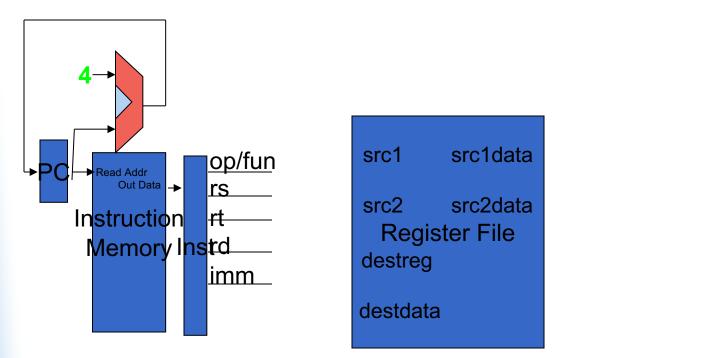

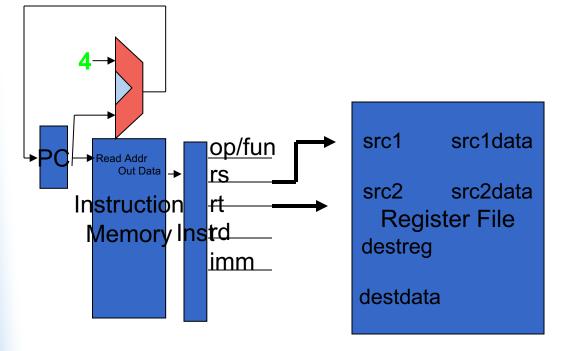

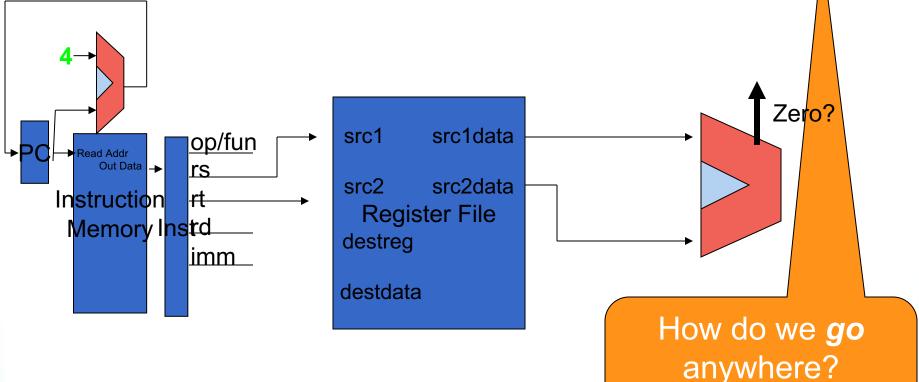

- 1) Design basic framework that is needed by all instructions

- 2) Build a computer for each operation individually

- 3) Add MUXs to choose between different operations

- 4) Add control signals to control the MUXs

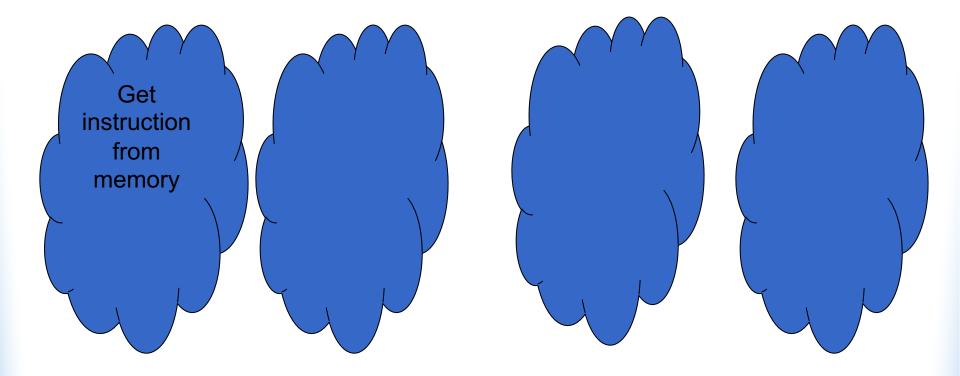

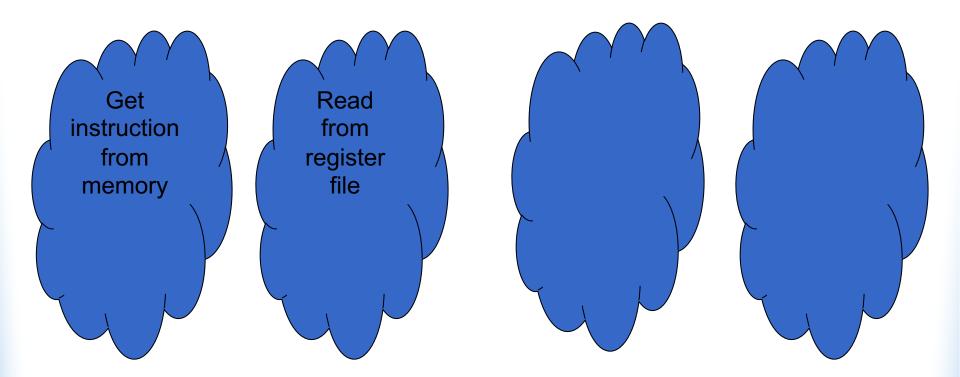

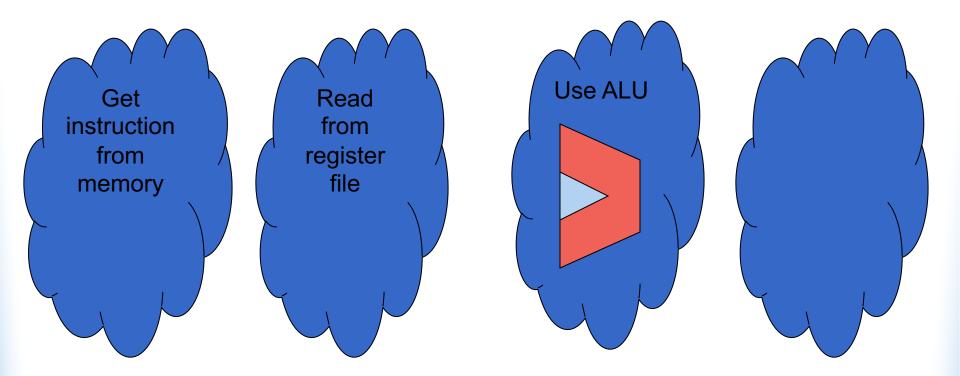

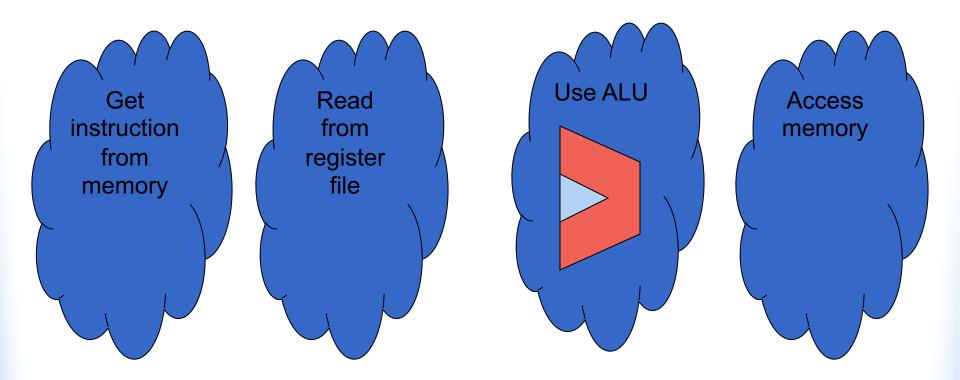

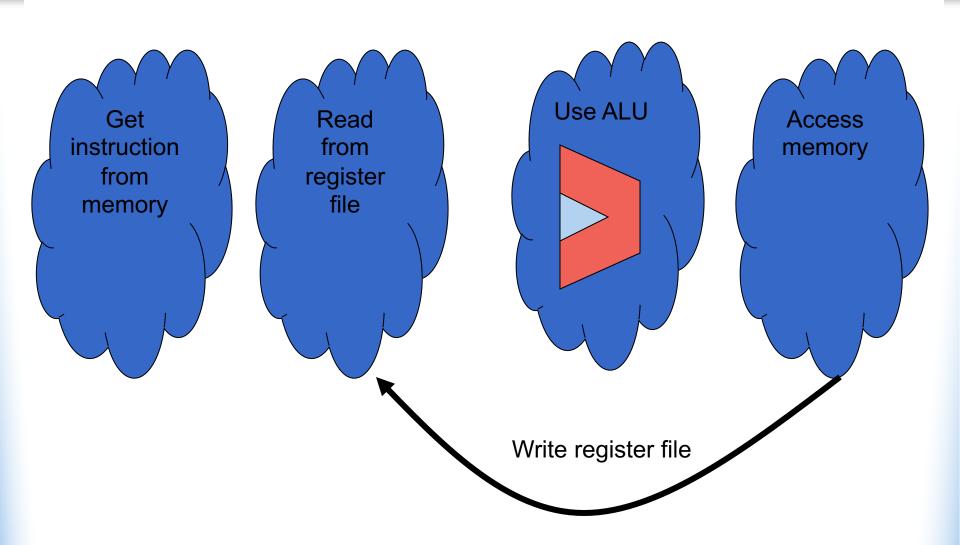

## **MIPS Steps**

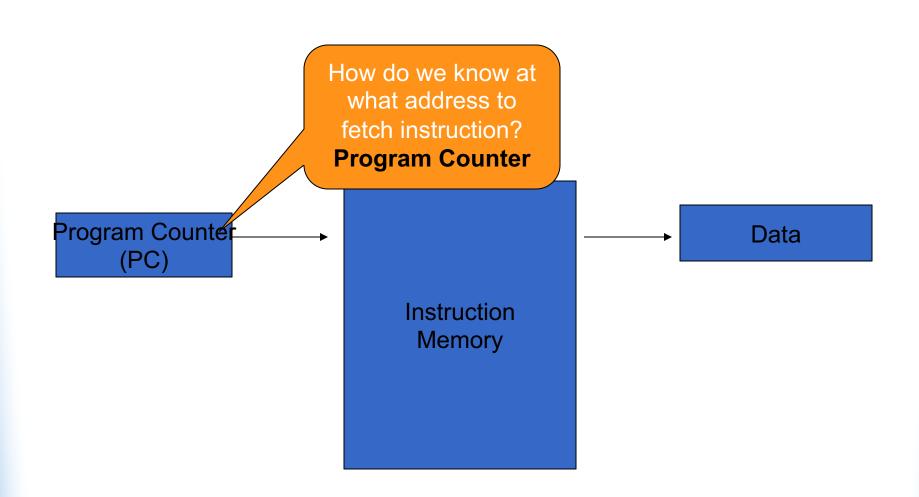

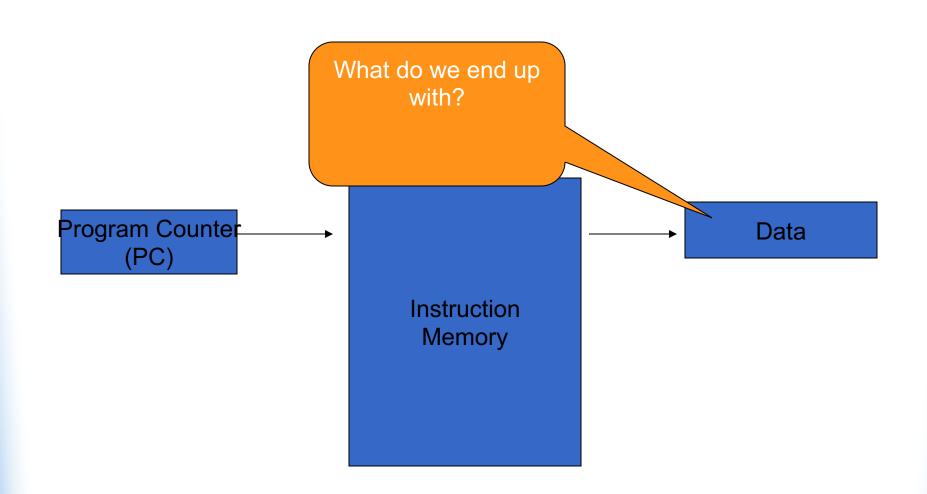

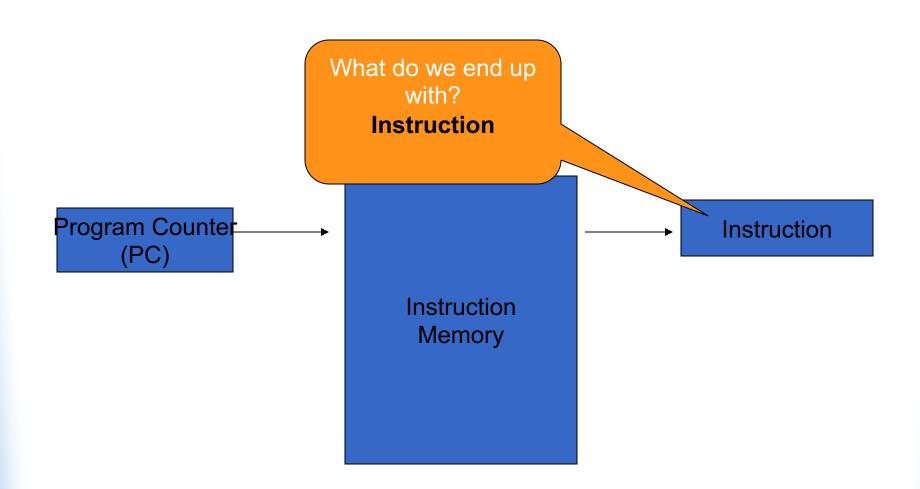

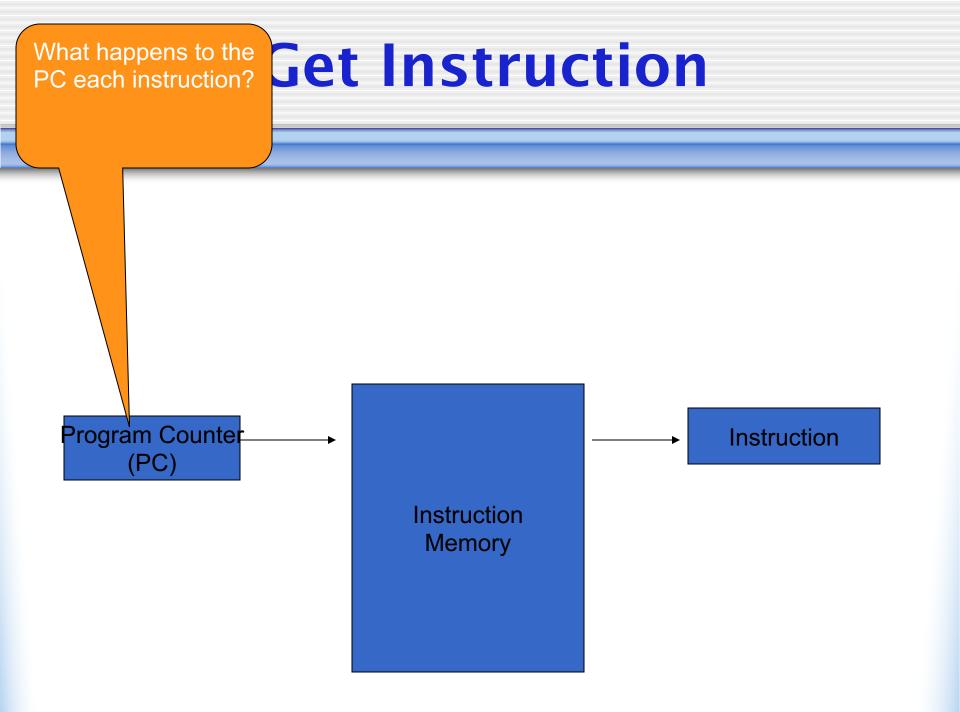

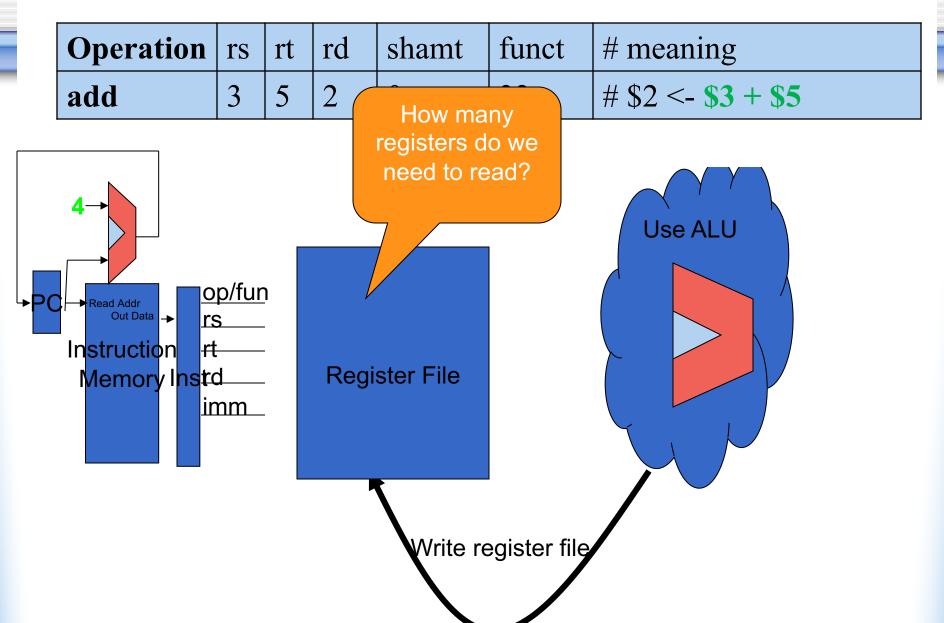

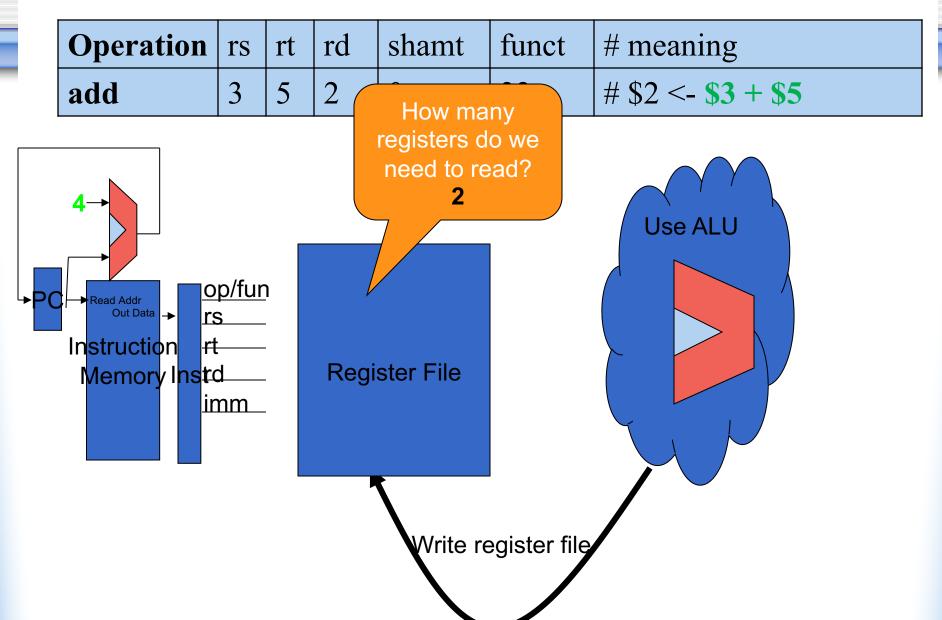

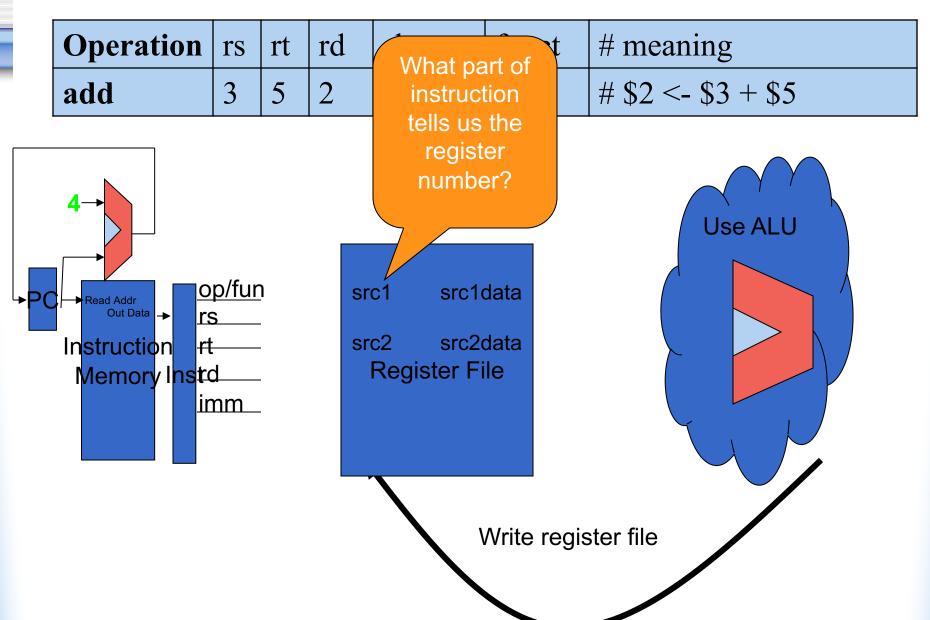

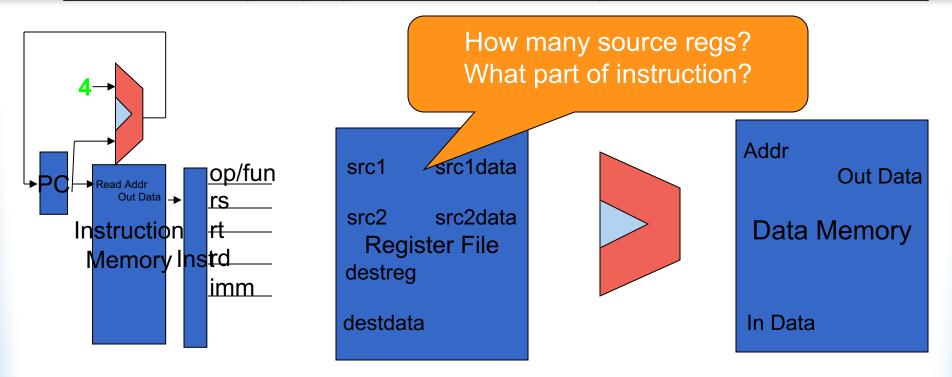

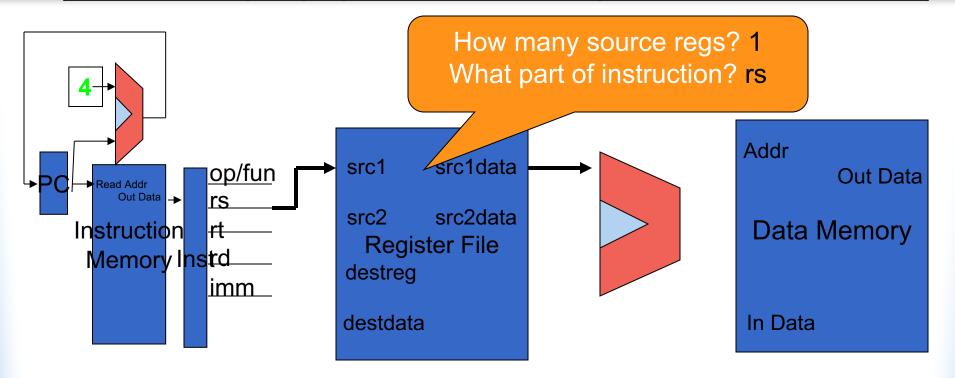

- Get an instruction from memory using the Program Counter (PC)

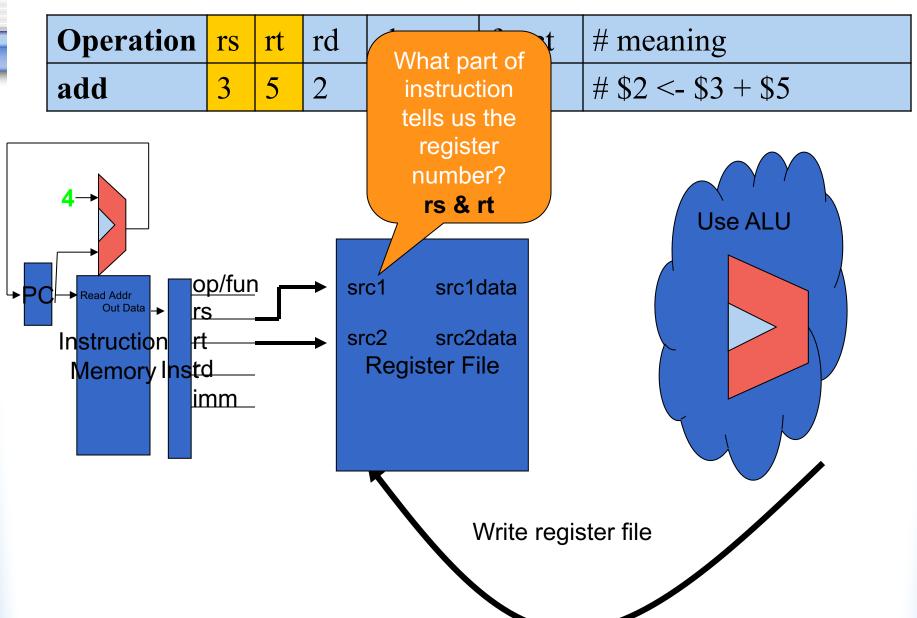

- Read one or two registers each instruction

- One register: addi, lw

- Two registers: add, sub, slt, sw, beq

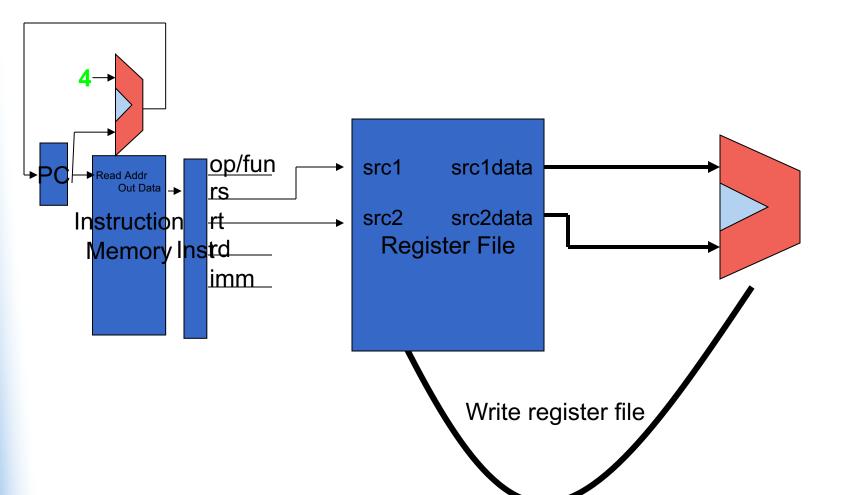

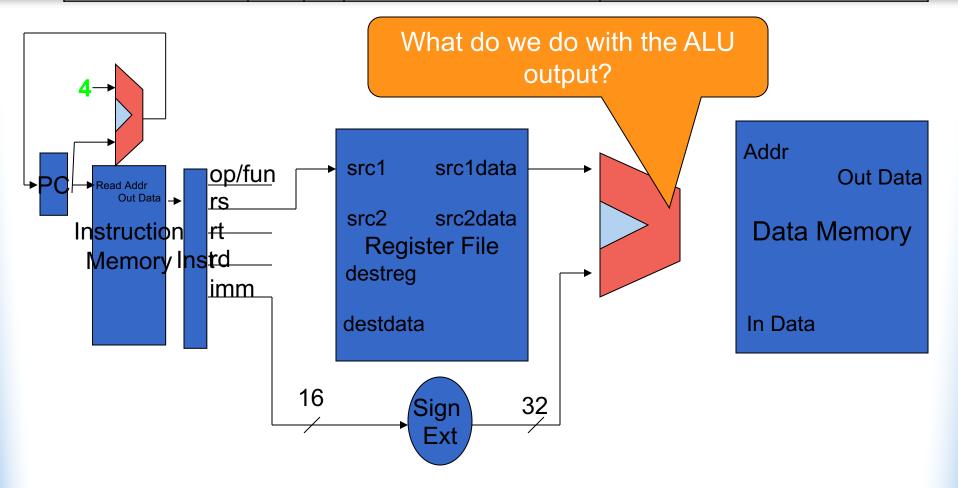

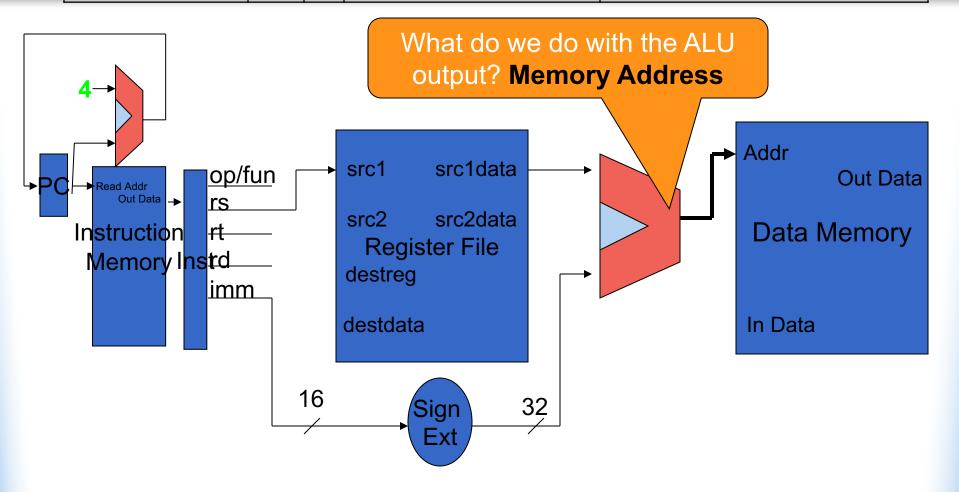

- All instructions use ALU after reading regs

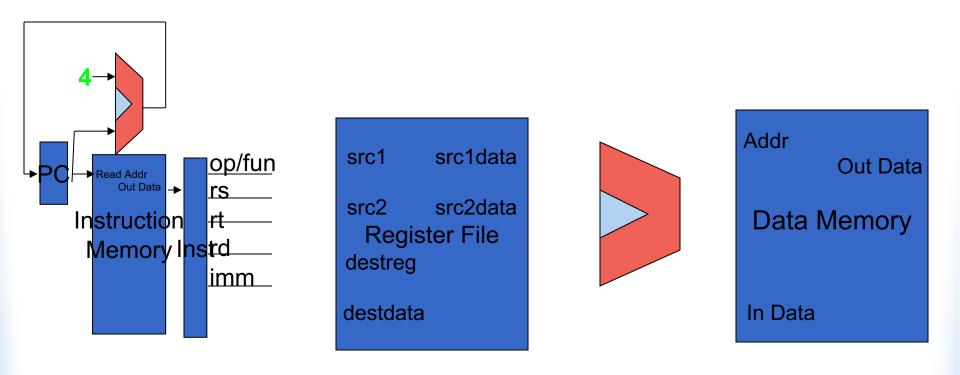

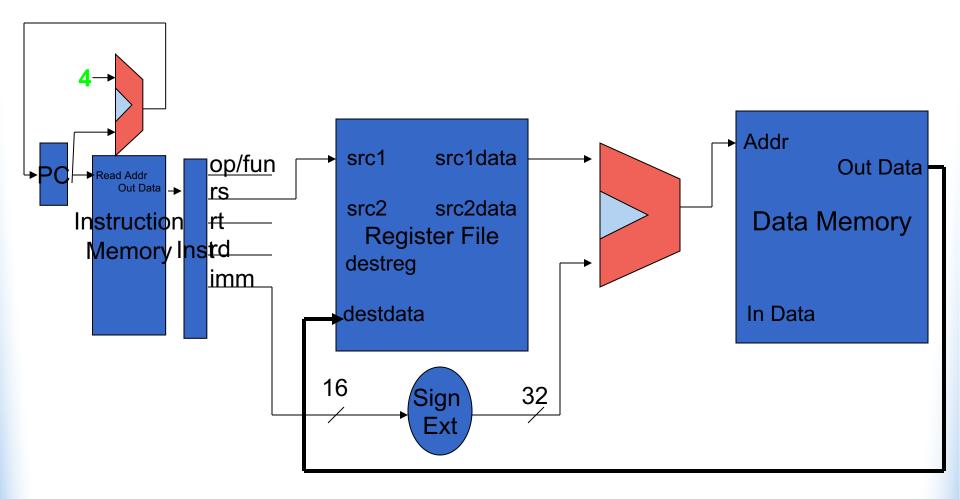

- Some instructions also access Memory

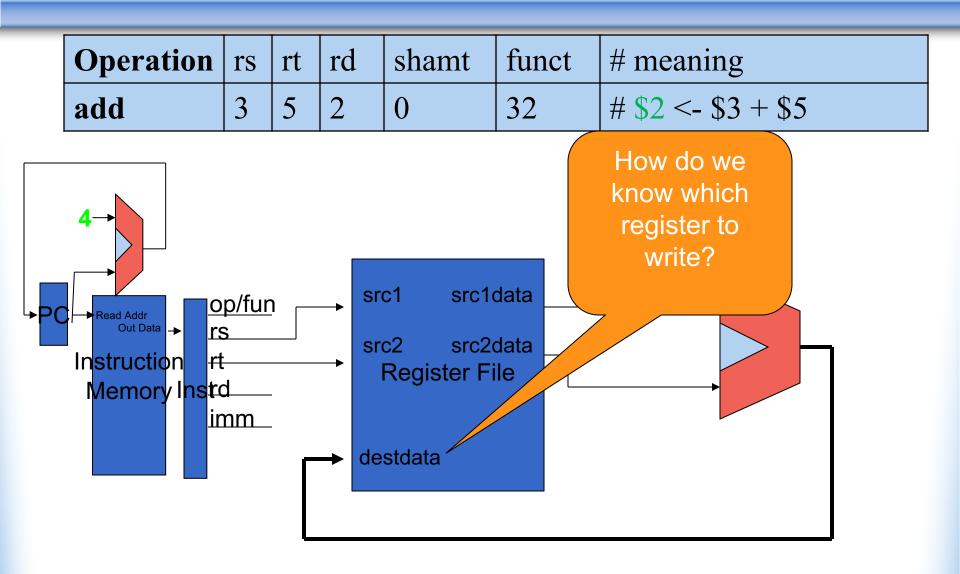

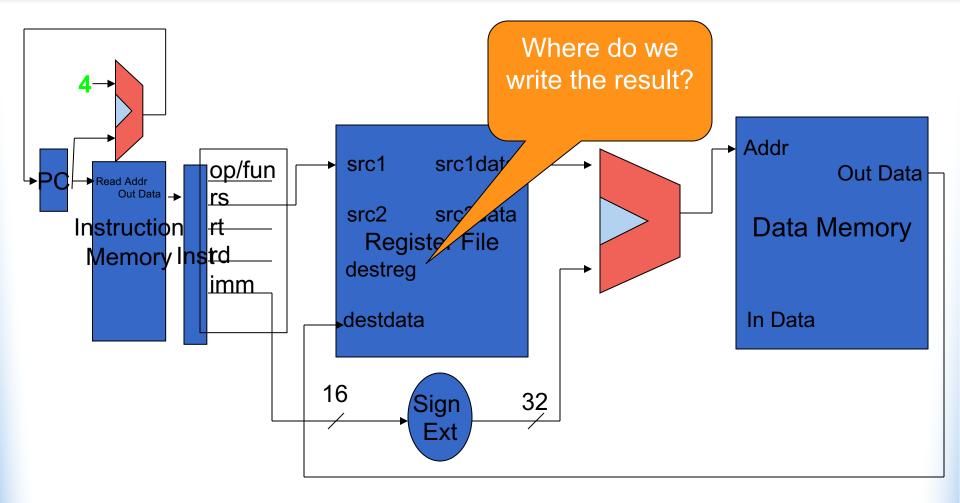

- Write result to Register file

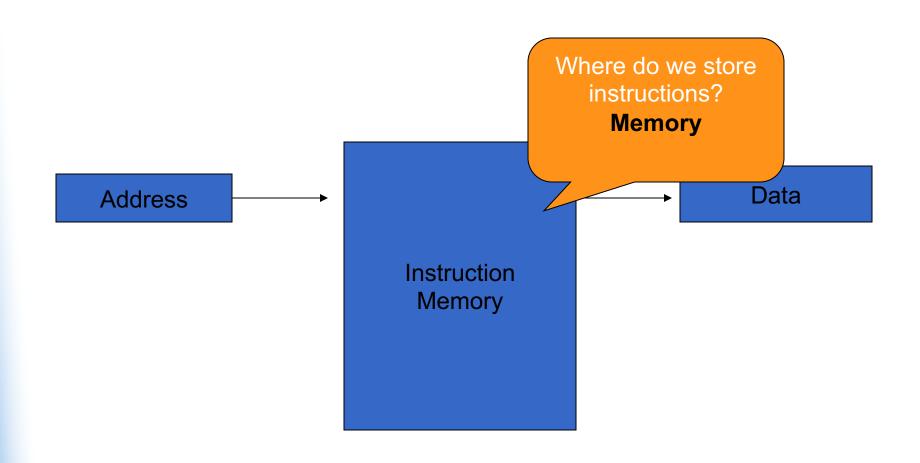

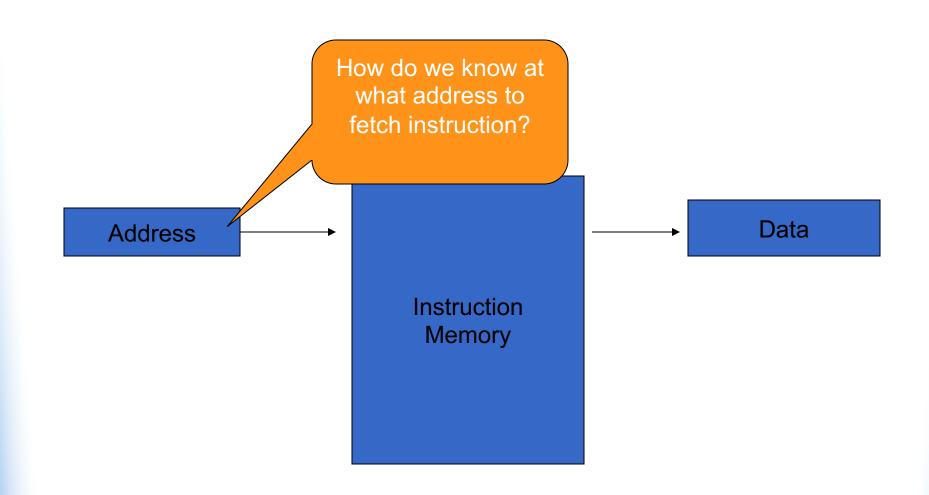

## What happens to the **Get Instruction**? PC each instruction? **Increment by 4B** Program Counter Instruction (PC) Instruction Memory

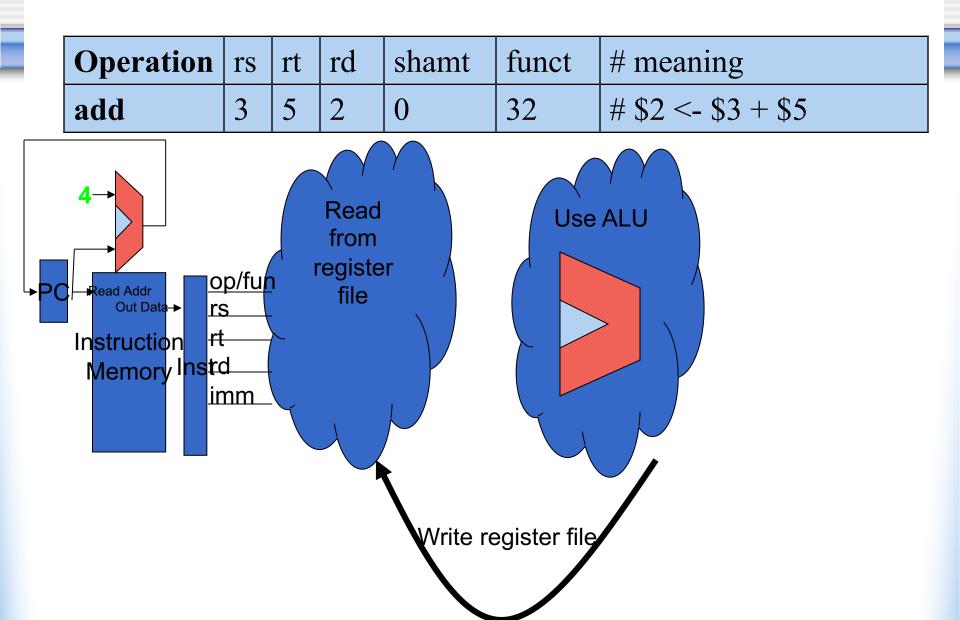

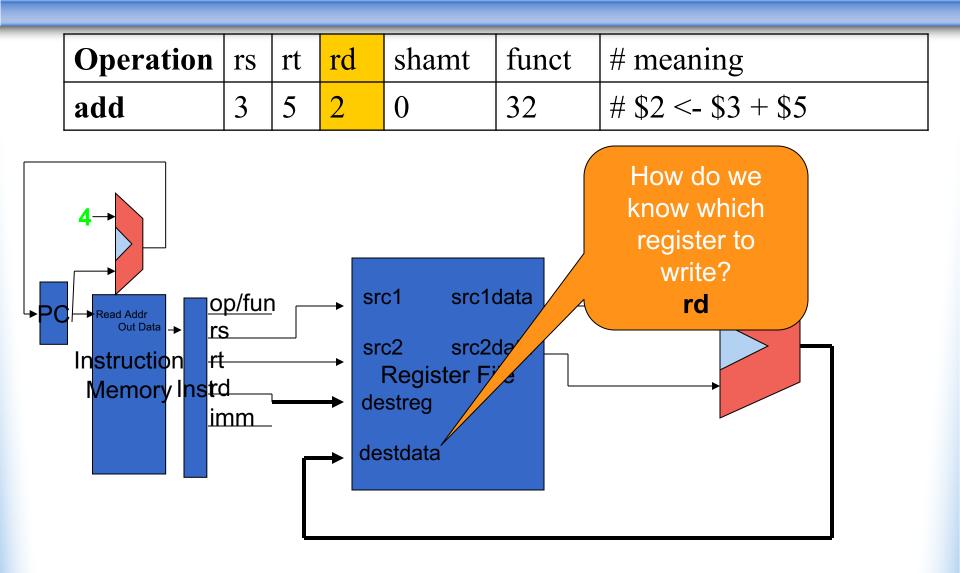

| Operation | rs | rt | rd | shamt | funct | # meaning          |  |

|-----------|----|----|----|-------|-------|--------------------|--|

| add       | 3  | 5  | 2  | 0     | 32    | # \$2 <- \$3 + \$5 |  |

| Operation | rs | rt | rd | shamt | funct | # meaning          |

|-----------|----|----|----|-------|-------|--------------------|

| add       | 3  | 5  | 2  | 0     | 32    | # \$2 <- \$3 + \$5 |

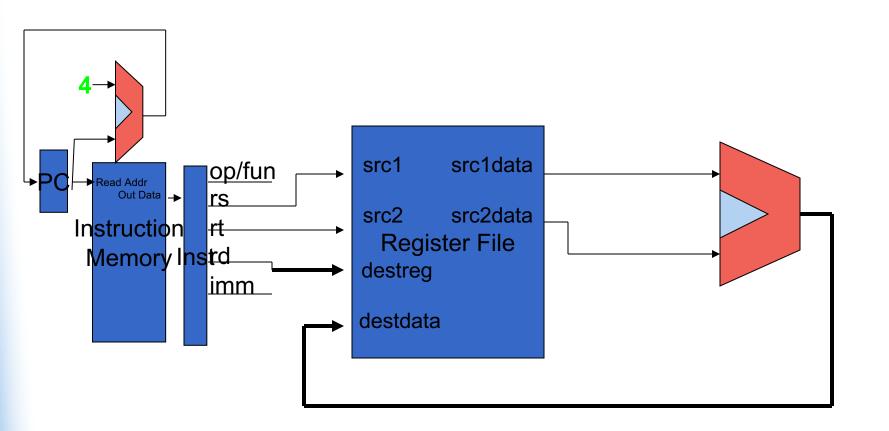

# What happens if instruction reads and writes same register?

| Operation | rs | rt | rd | shamt | funct | # meaning          |

|-----------|----|----|----|-------|-------|--------------------|

| add       | 3  | 5  | 3  | 0     | 32    | # \$3 <- \$3 + \$5 |

# What happens if instruction reads and writes same register?

| Operation | rs | rt | rd | shamt | funct | # meaning          |

|-----------|----|----|----|-------|-------|--------------------|

| add       | 3  | 5  | 3  | 0     | 32    | # \$3 <- \$3 + \$5 |

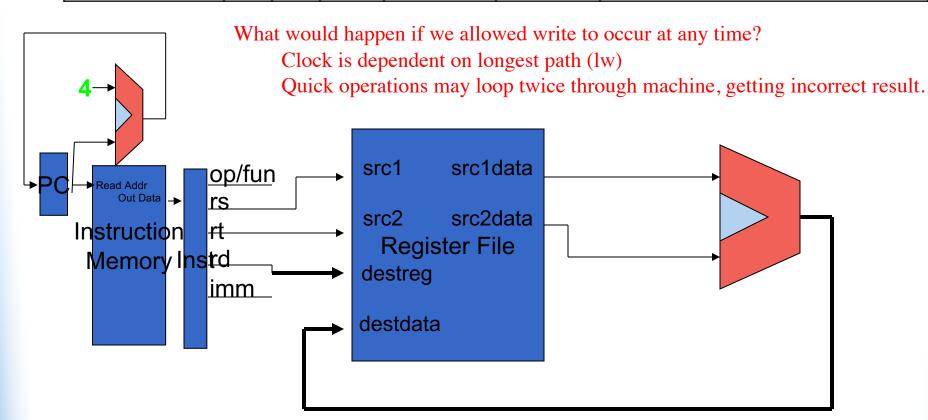

## **Reading/Write Registers**

- When does register get written?

- At the end of the clock cycle

- Edge-triggered circuits

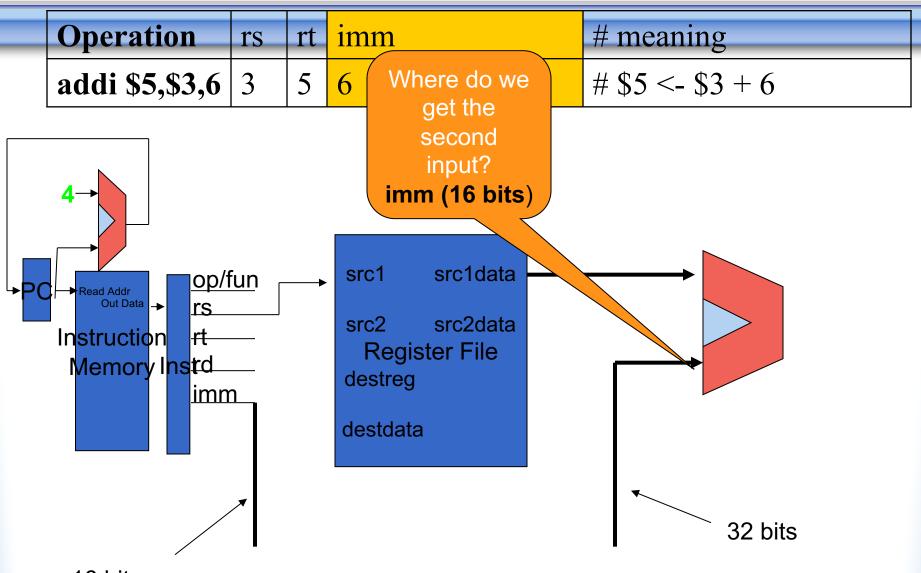

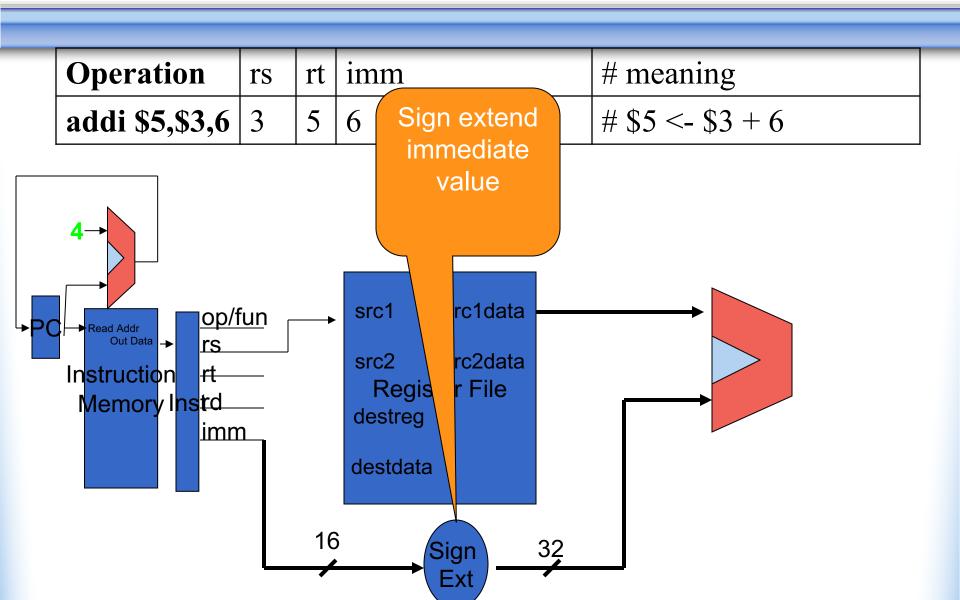

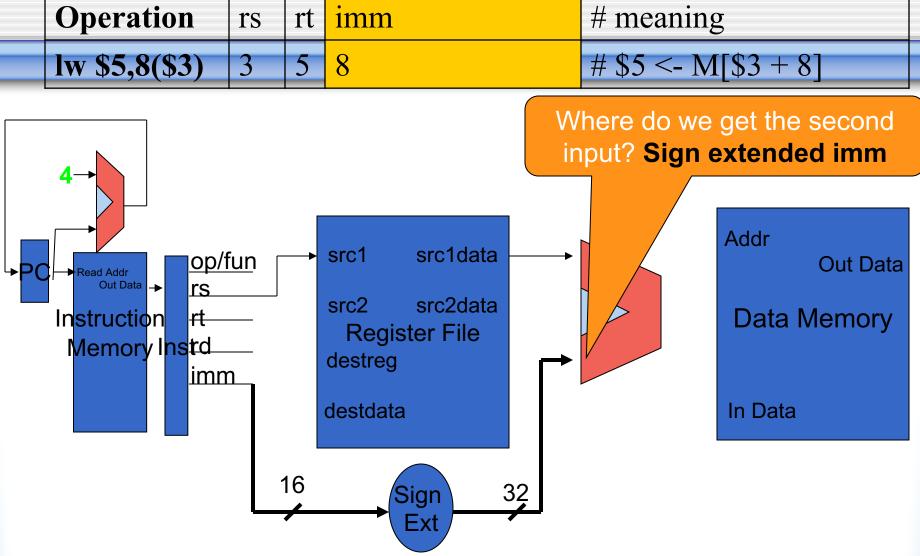

16 bits

## **Sign Extension**

- How do we go from 16-bit number to 32-bit number?

- How about 4-bit to 8-bit.

- 0111 = 7 = 00000111

- 1110 = -2 = 11111110

- Take the top bit and copy it to all the other bits

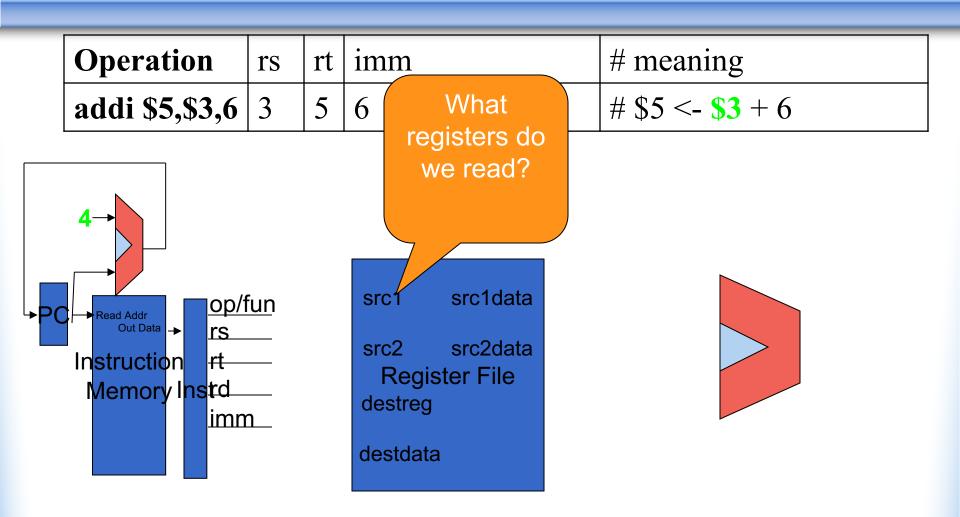

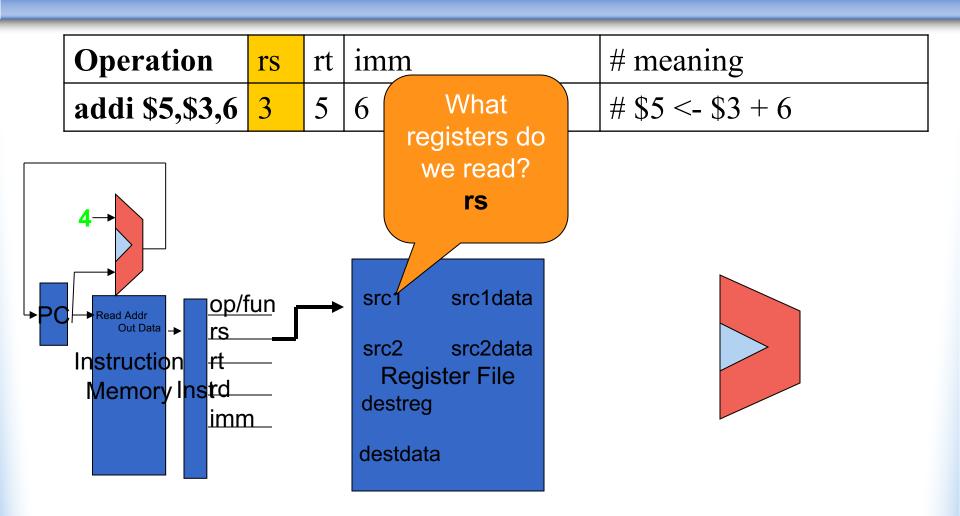

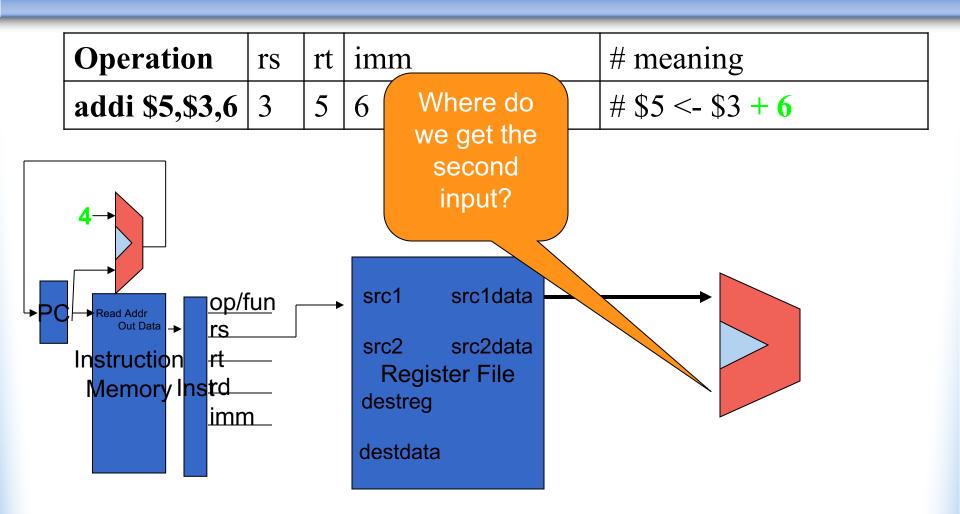

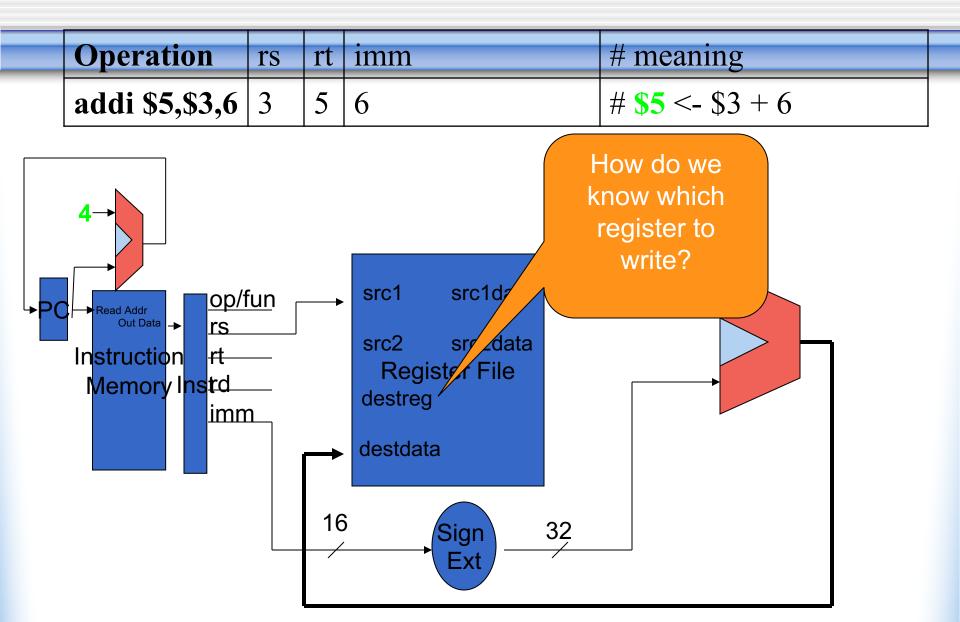

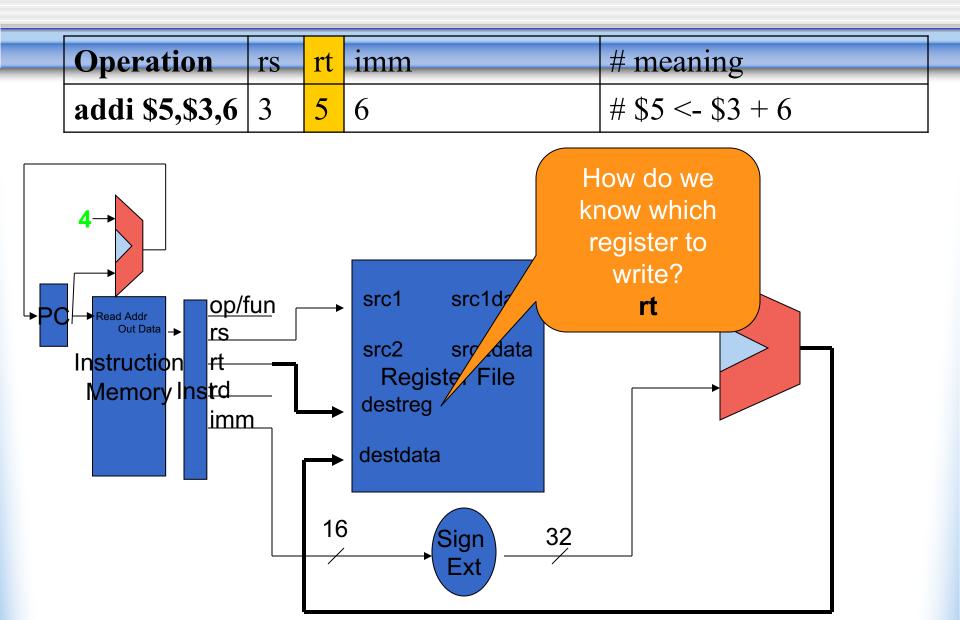

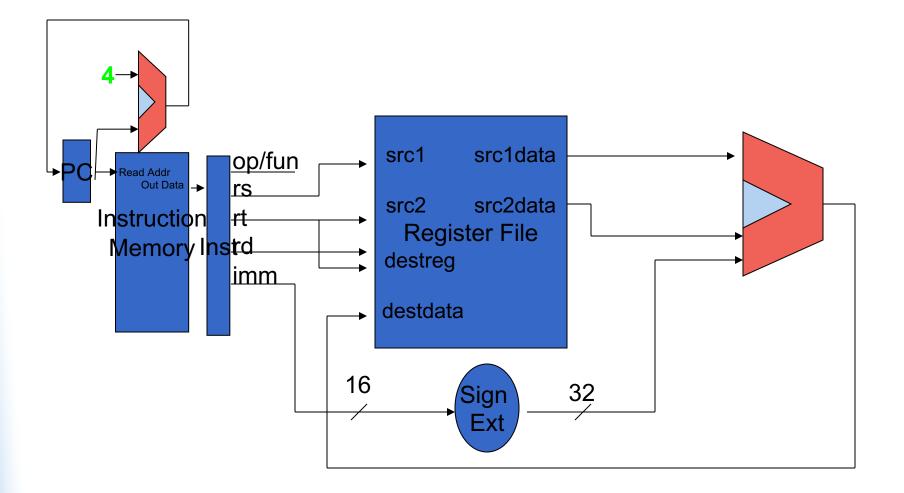

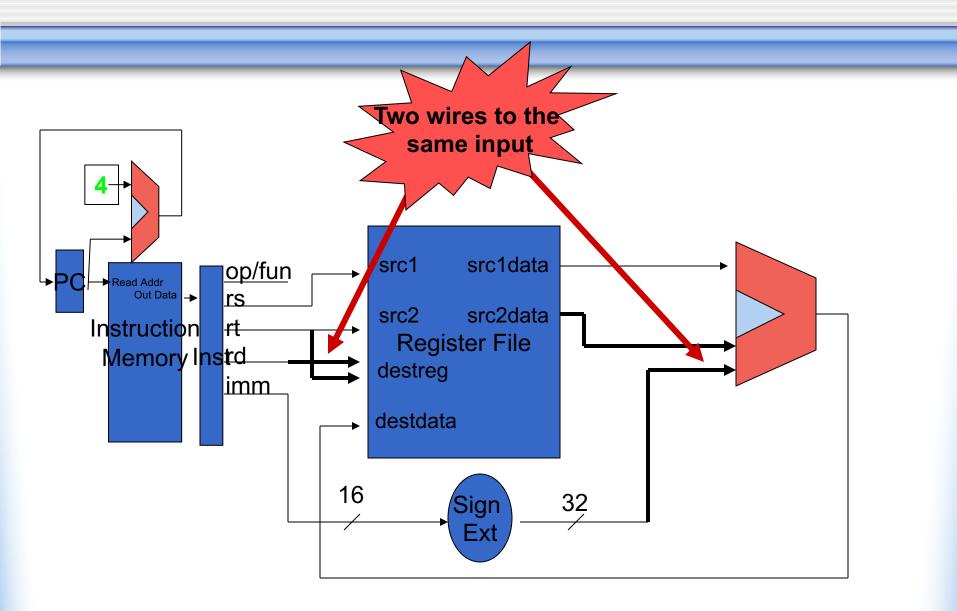

# "Addi" Instruction

# "Addi" Instruction

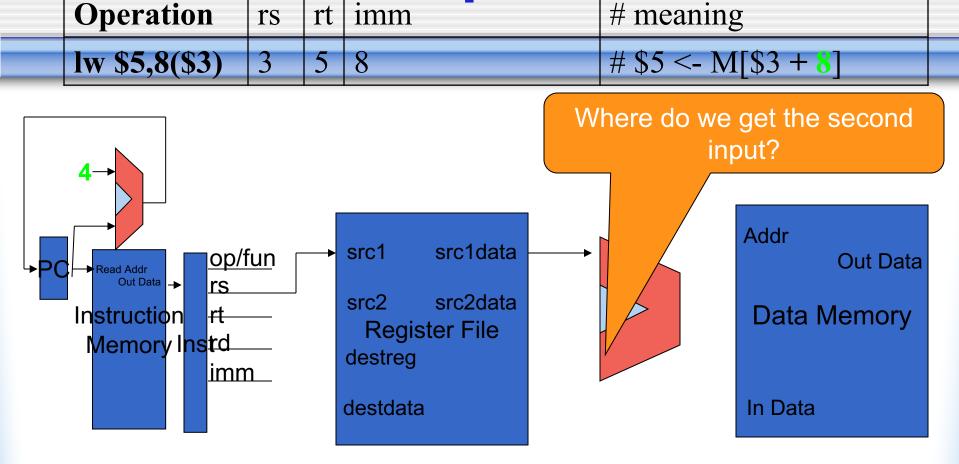

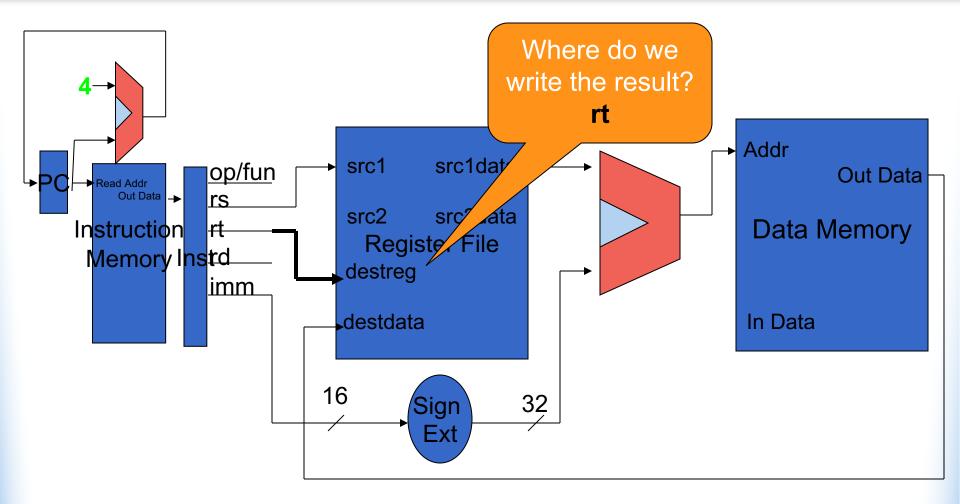

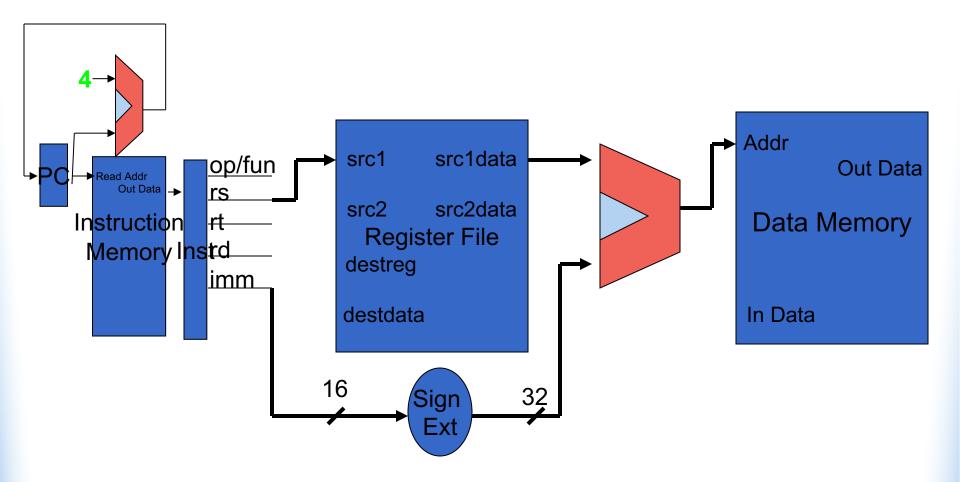

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| lw \$5,8(\$3) | 3  | 5  | 8   | # \$5 <- M[\$3 + 8] |  |

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| lw \$5,8(\$3) | 3  | 5  | 8   | # \$5 <- M[\$3 + 8] |  |

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| lw \$5,8(\$3) | 3  | 5  | 8   | # \$5 <- M[\$3 + 8] |  |

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| lw \$5,8(\$3) | 3  | 5  | 8   | # \$5 <- M[\$3 + 8] |  |

| Operation     | rs | rt | imm | # meaning           |

|---------------|----|----|-----|---------------------|

| lw \$5,8(\$3) | 3  | 5  | 8   | # \$5 <- M[\$3 + 8] |

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| lw \$5,8(\$3) | 3  | 5  | 8   | # \$5 <- M[\$3 + 8] |  |

| Operation     | rs | rt | imm | # meaning                  |

|---------------|----|----|-----|----------------------------|

| lw \$5,8(\$3) | 3  | 5  | 8   | # <b>\$5</b> <- M[\$3 + 8] |

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| lw \$5,8(\$3) | 3  | 5  | 8   | # \$5 <- M[\$3 + 8] |  |

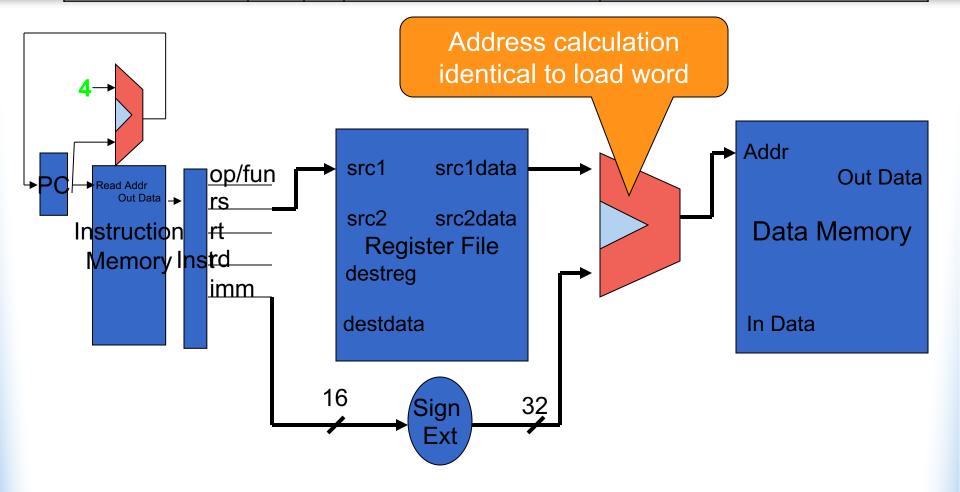

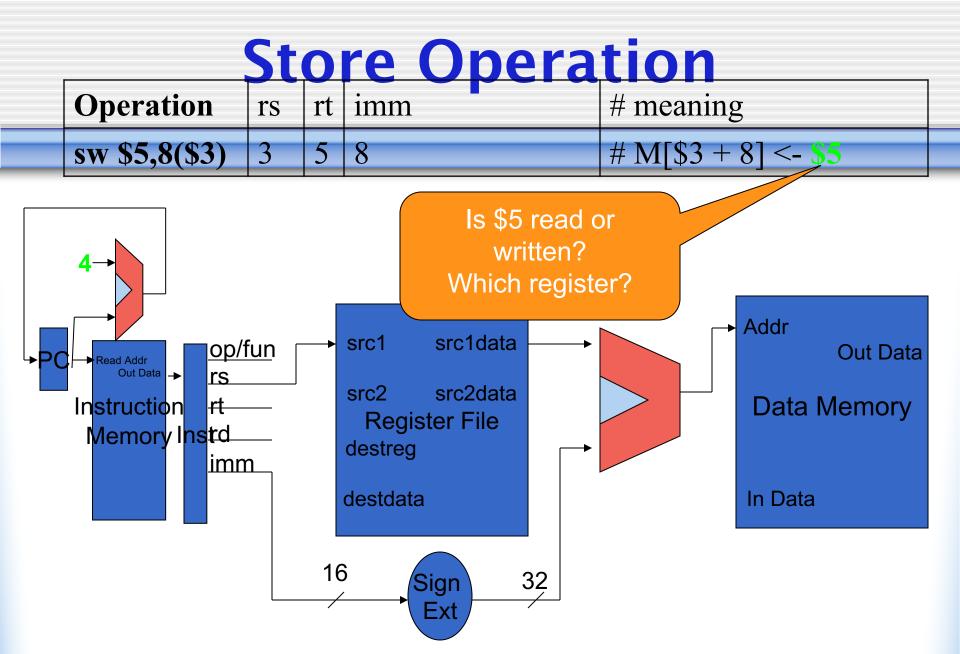

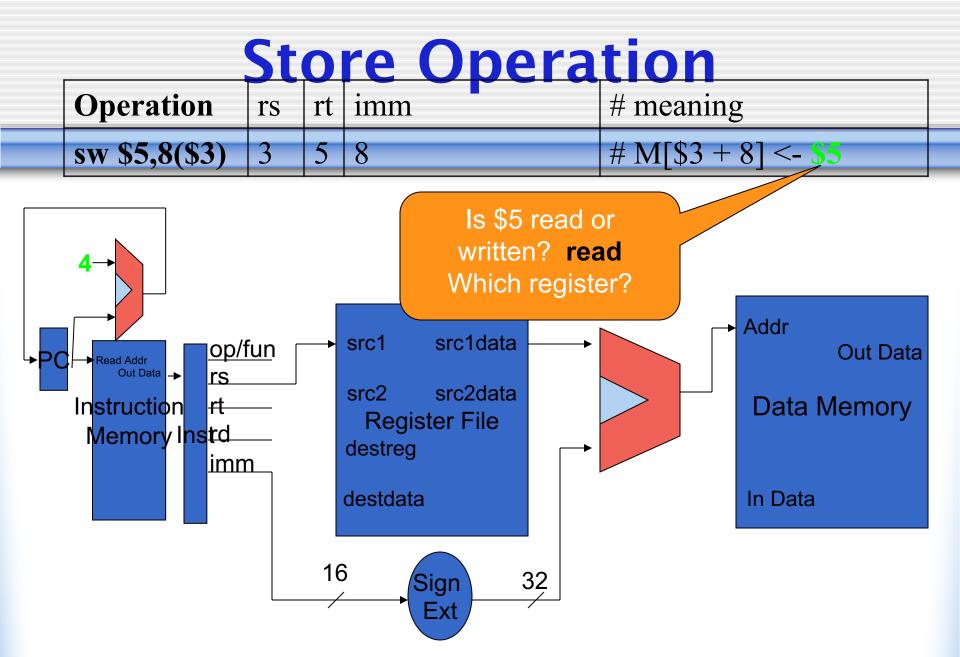

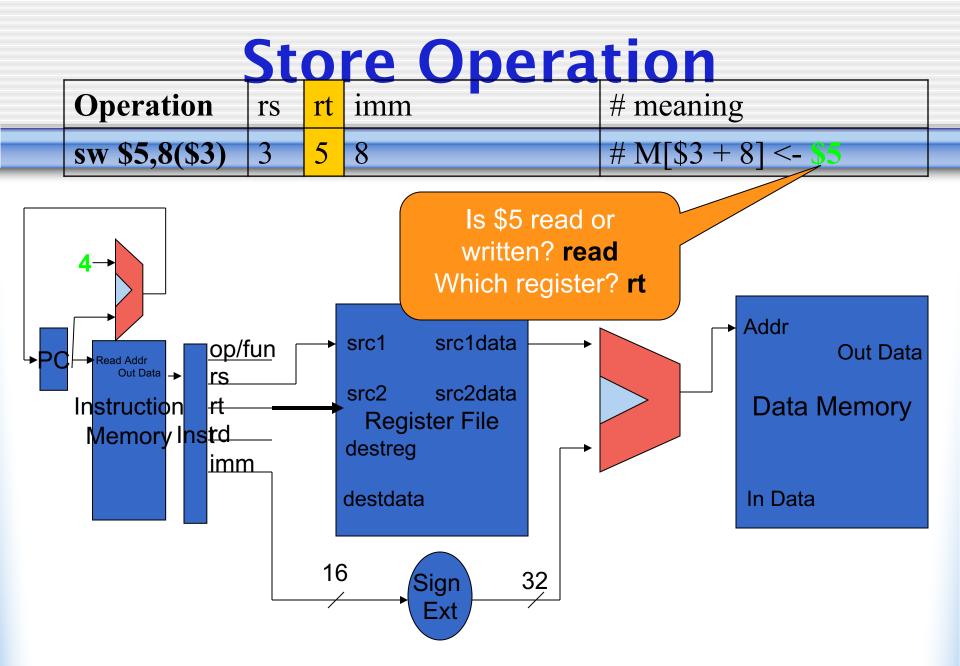

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| sw \$5,8(\$3) | 3  | 5  | 8   | # M[\$3 + 8] <- \$5 |  |

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| sw \$5,8(\$3) | 3  | 5  | 8   | # M[\$3 + 8] <- \$5 |  |

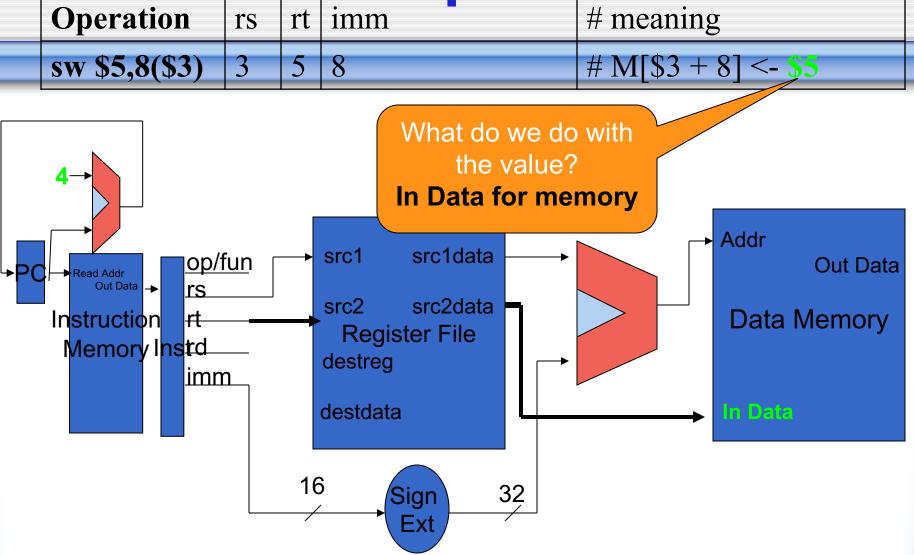

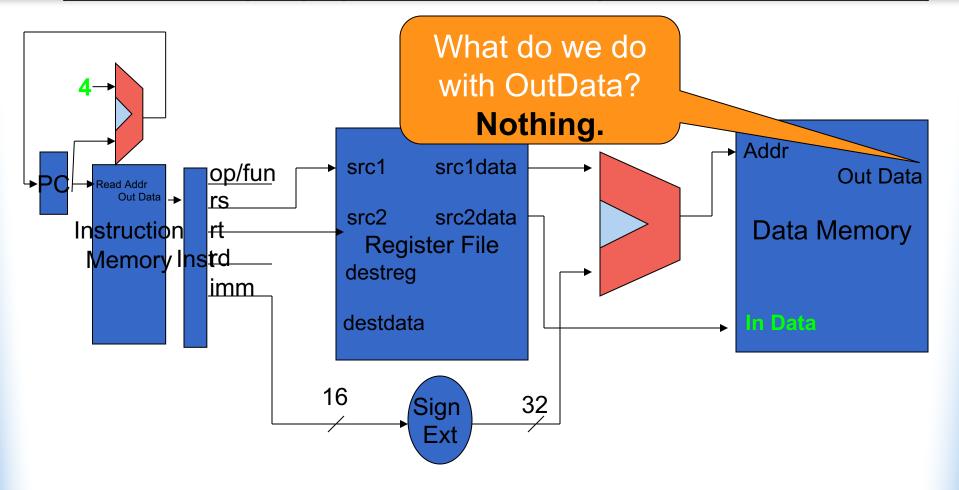

#### **Store Operation Operation** # meaning rt rs imm sw \$5,8(\$3) 3 # M[\$3 + 8] <- \$5 5 8 What do we do with the value? Addr src1 src1data <u>op/fun</u> **Out Data** DC Read Addr Out Data rs src2 src2data Data Memory Instruction Irt **Register File** Memory Instd

32

In Data

destreg

destdata

Sign

Ext

16

limm

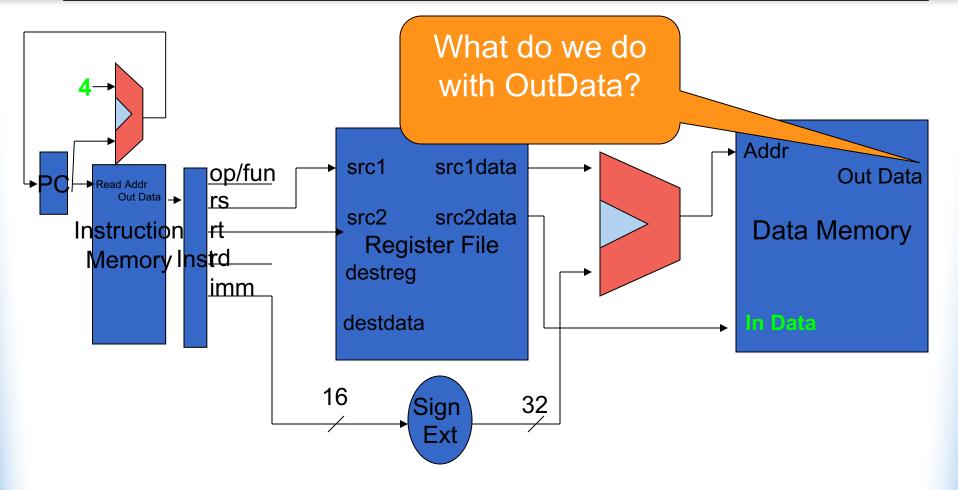

| Operation     | rs | rt | imm | # meaning           |  |

|---------------|----|----|-----|---------------------|--|

| sw \$5,8(\$3) | 3  | 5  | 8   | # M[\$3 + 8] <- \$5 |  |

| Operation     | rs | rt | imm | # meaning           |

|---------------|----|----|-----|---------------------|

| sw \$5,8(\$3) | 3  | 5  | 8   | # M[\$3 + 8] <- \$5 |

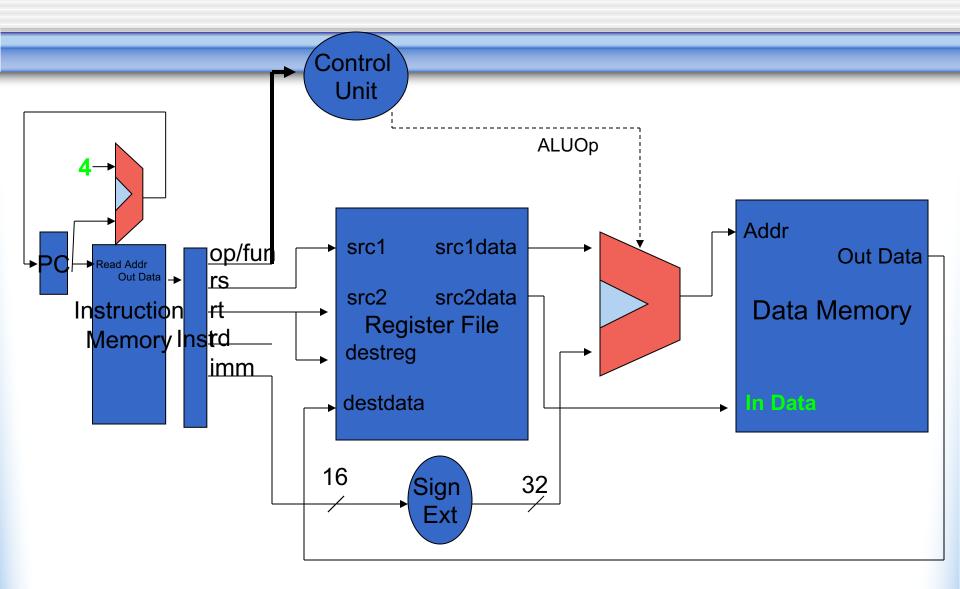

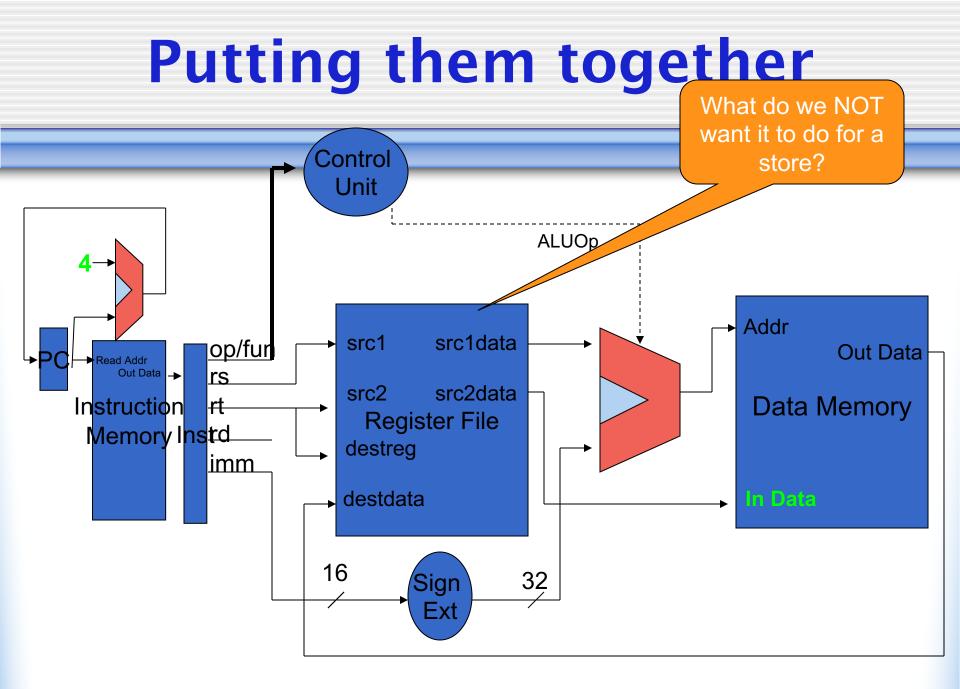

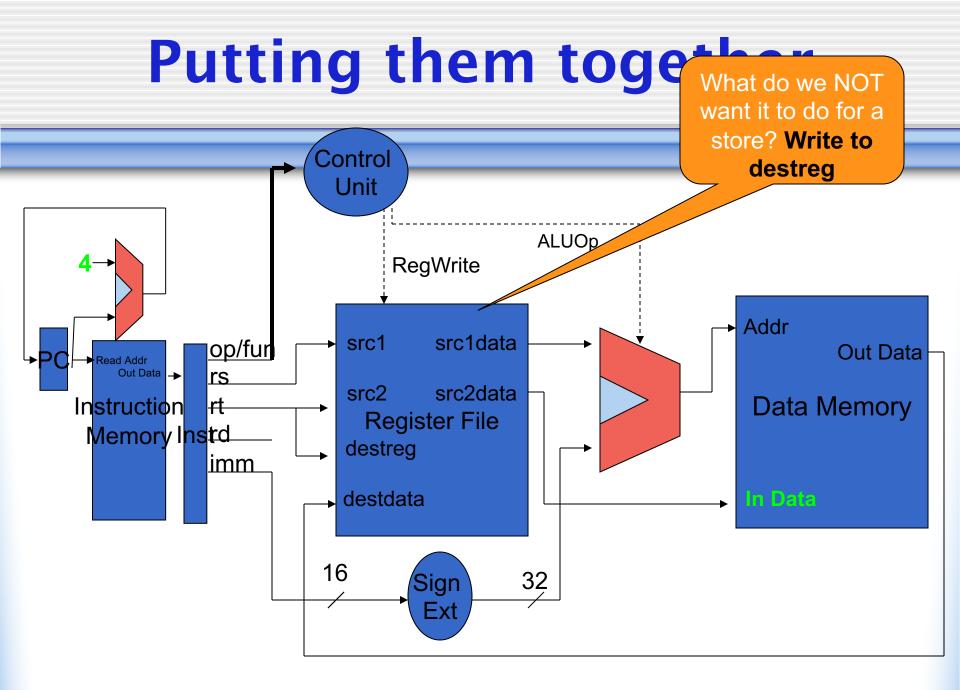

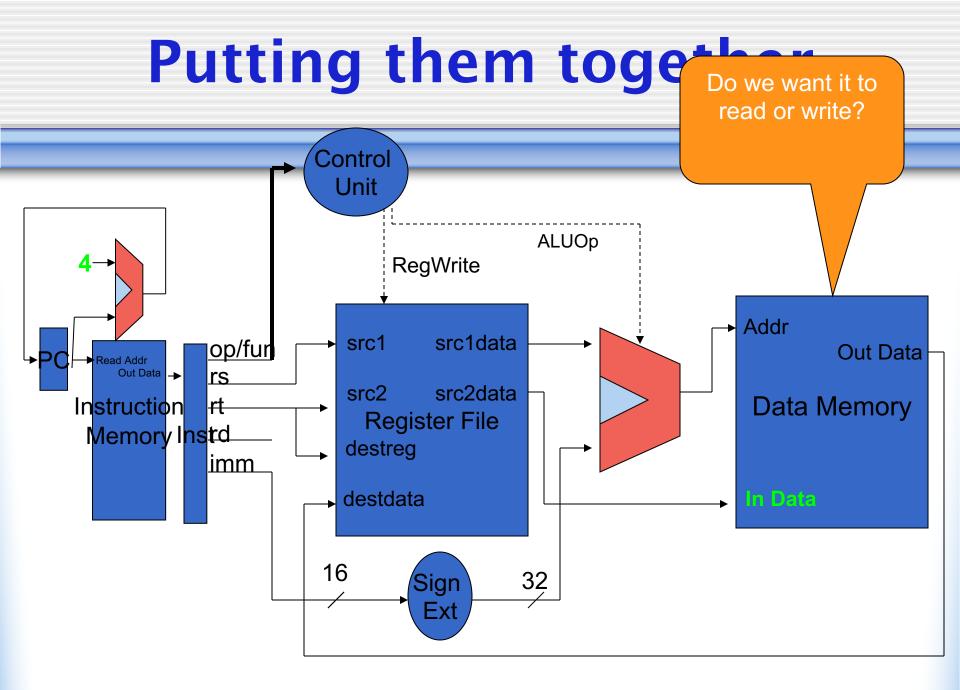

#### Do we want it to **Putting them togeth** read or write? **Depends on** opcode Control MemWr Unit MemRd **ALUOp** RegWrite Addr src1 src1data op/fur **Out Data** כ Read Addr Out Data rs src2 src2data **Data Memory** Instruction rt **Register File** Memory Instd destreg limm destdata In Data

32

Sign

Ext

16

| <b>661</b> |        |       |

|------------|--------|-------|

| ned ~      | Instru | ction |

|            |        |       |

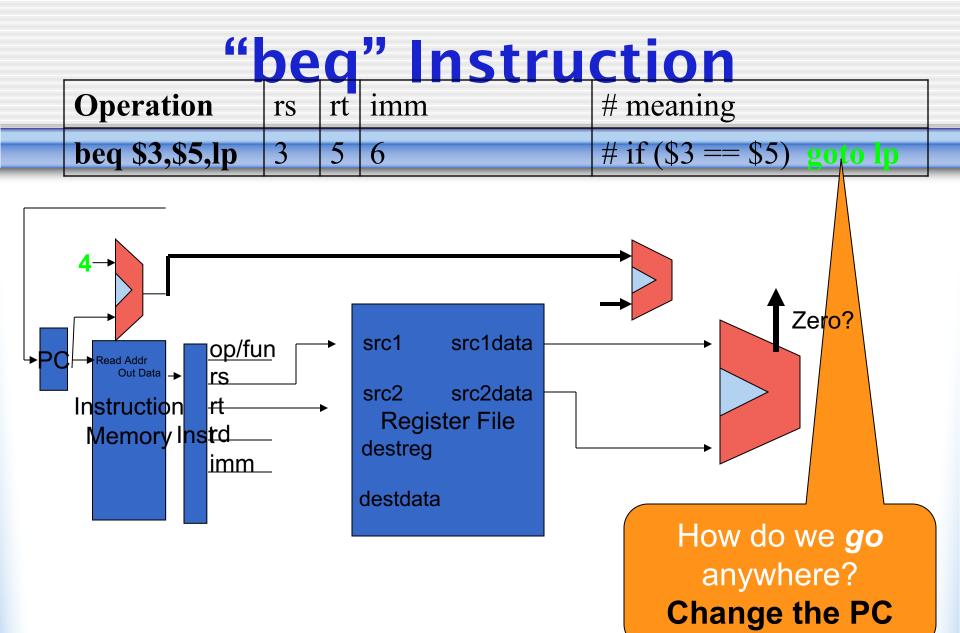

| Operation      | rs | rt | imm | # meaning                 |  |

|----------------|----|----|-----|---------------------------|--|

| beq \$3,\$5,lp | 3  | 5  | 6   | # if (\$3 == \$5) goto lp |  |

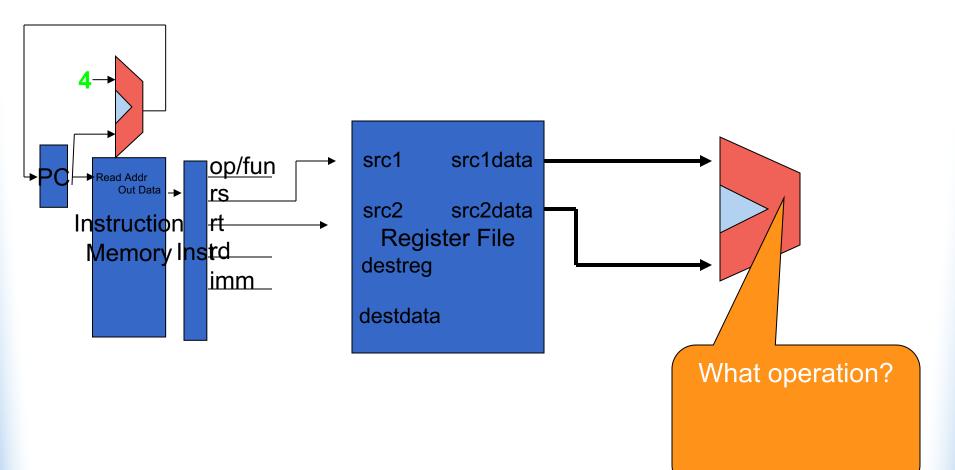

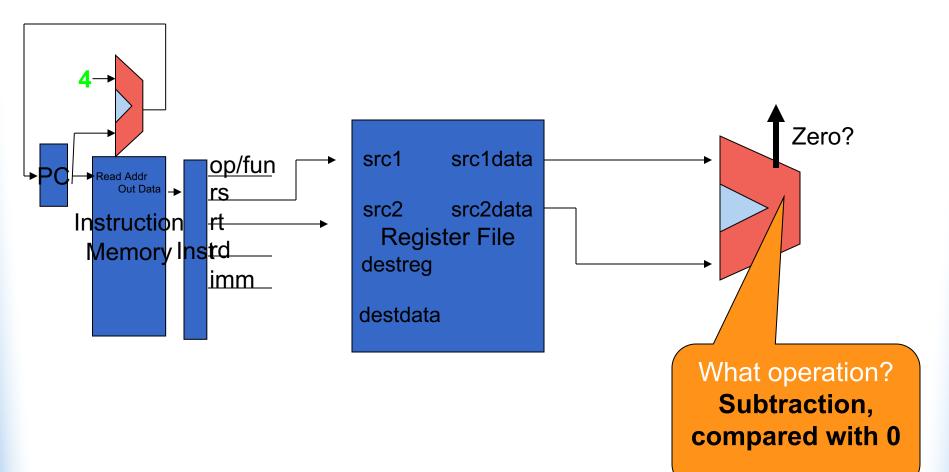

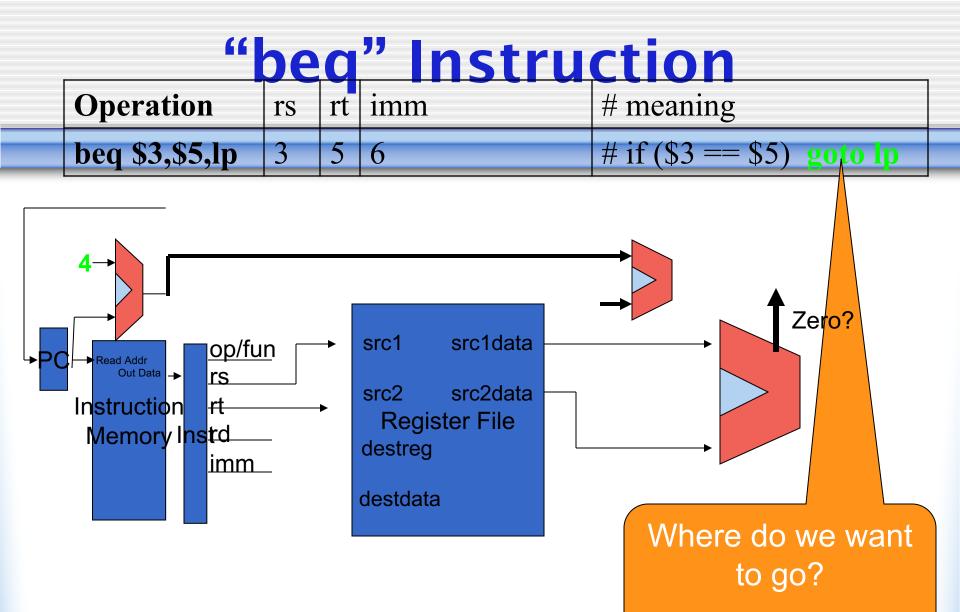

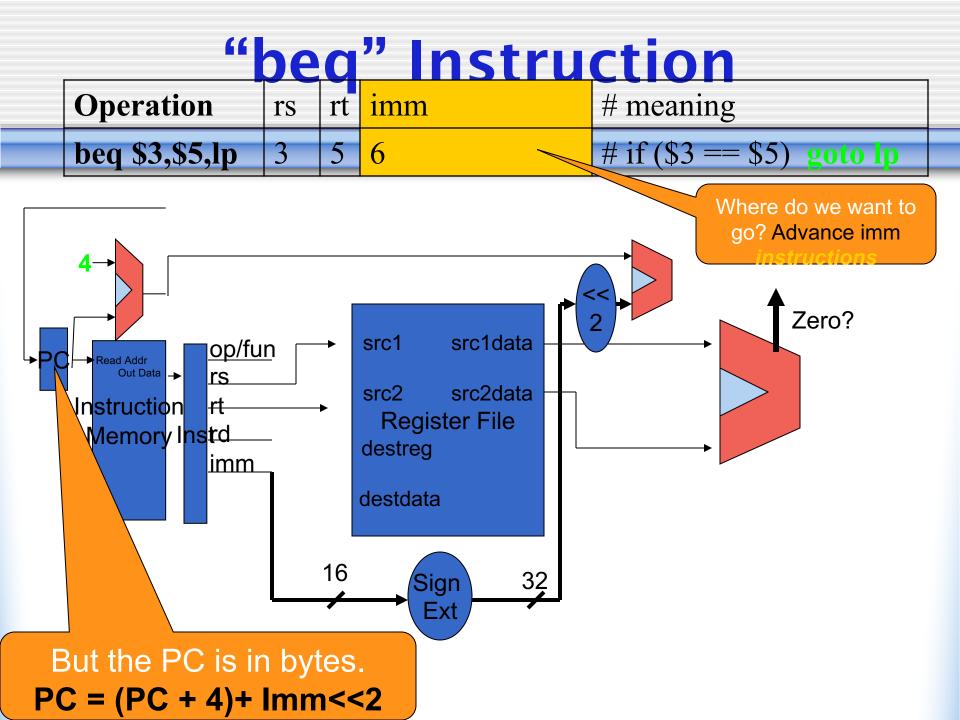

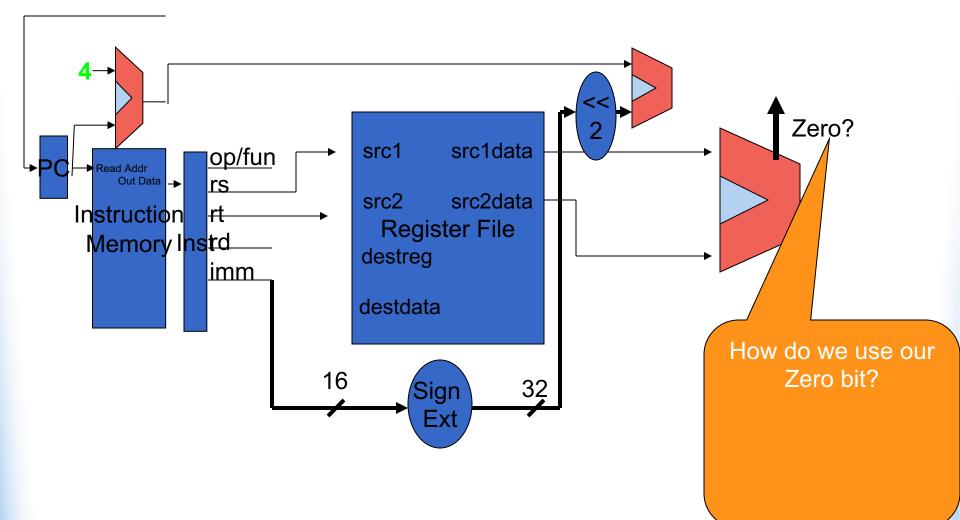

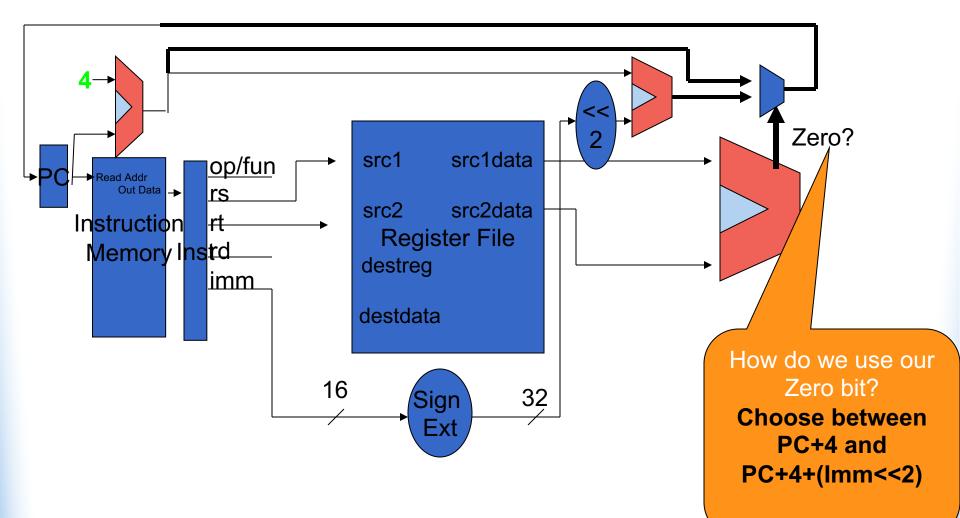

## "beg" Instruction

| Operation      | rs | rt | imm | # meaning                 |  |

|----------------|----|----|-----|---------------------------|--|

| beq \$3,\$5,lp | 3  | 5  | 6   | # if (\$3 == \$5) goto lp |  |

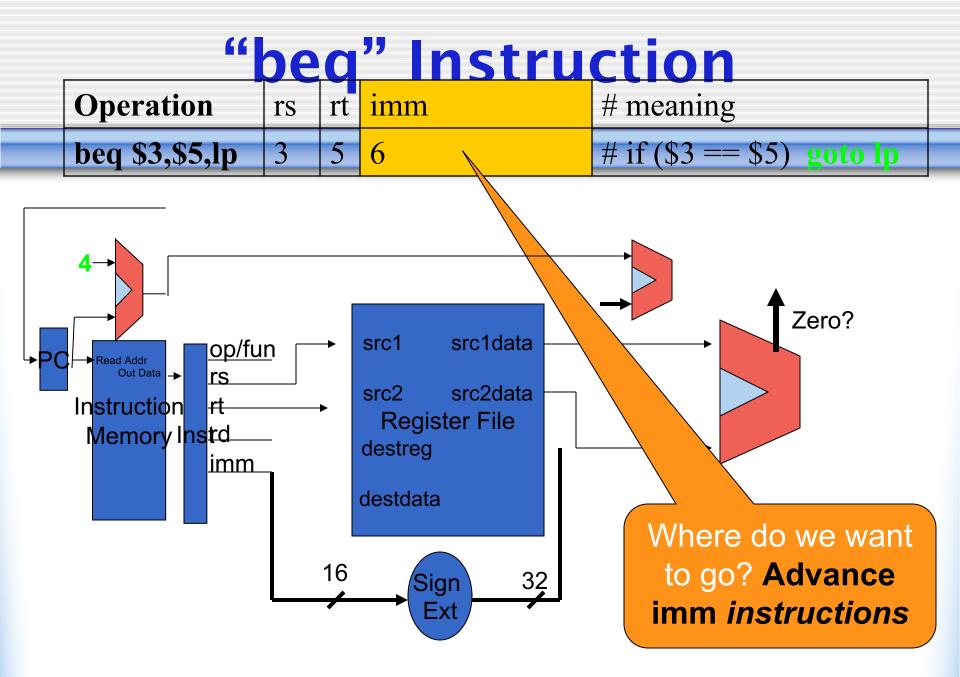

#### "beg" Instruction

| Operation      | rs | rt | imm | # meaning                  |  |

|----------------|----|----|-----|----------------------------|--|

| beq \$3,\$5,lp | 3  | 5  | 6   | # if (\$3 === \$5) goto lp |  |

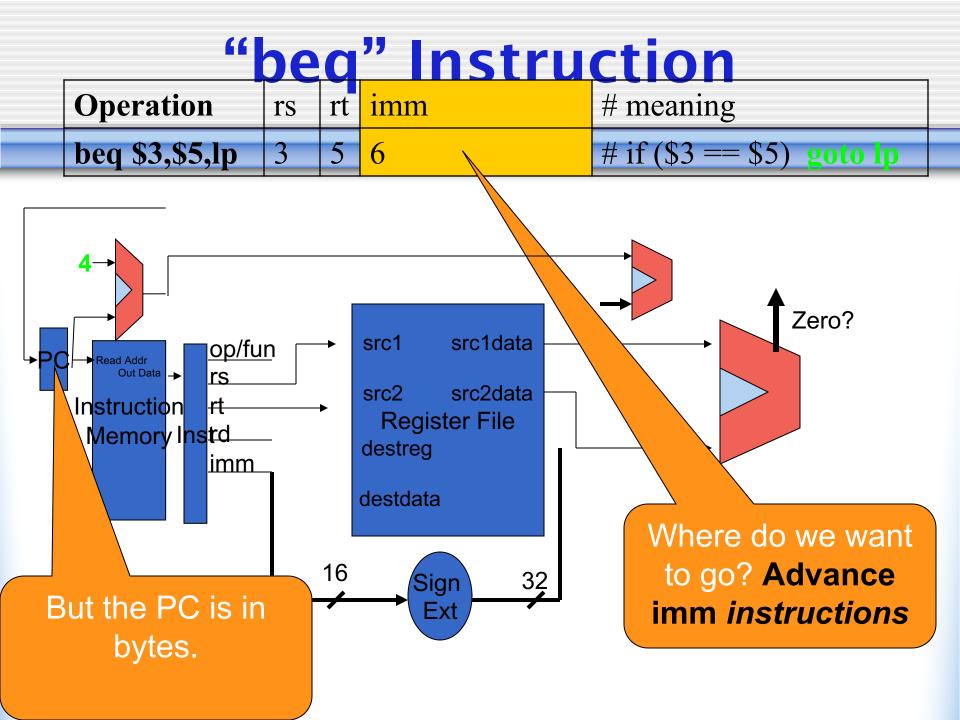

#### "beg" Instruction

| Operation      | rs | rt | imm | # meaning                 |  |

|----------------|----|----|-----|---------------------------|--|

| beq \$3,\$5,lp | 3  | 5  | 6   | # if (\$3 == \$5) goto lp |  |

# "beg" Instruction Operation rs rt imm # meaning beq \$3,\$5,lp 3 5 6 # if (\$3 == \$5) goto lp

#### "beg" Instruction

| Operation      | rs | rt | imm | # meaning                 |  |

|----------------|----|----|-----|---------------------------|--|

| beq \$3,\$5,lp | 3  | 5  | 6   | # if (\$3 == \$5) goto lp |  |

# "beq" Instruction Operation rs rt imm # meaning beq \$3,\$5,lp 3 5 6 # if (\$3 == \$5) goto lp

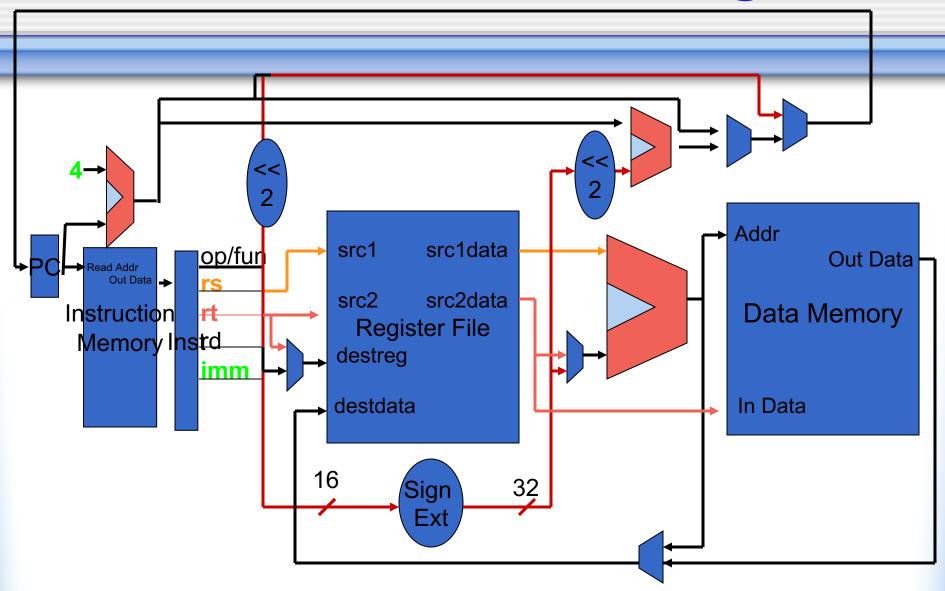

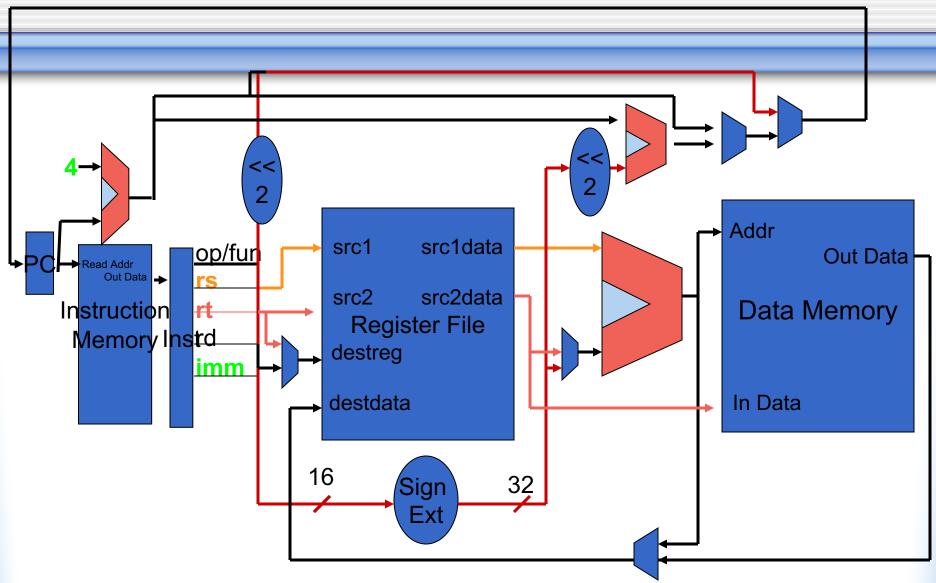

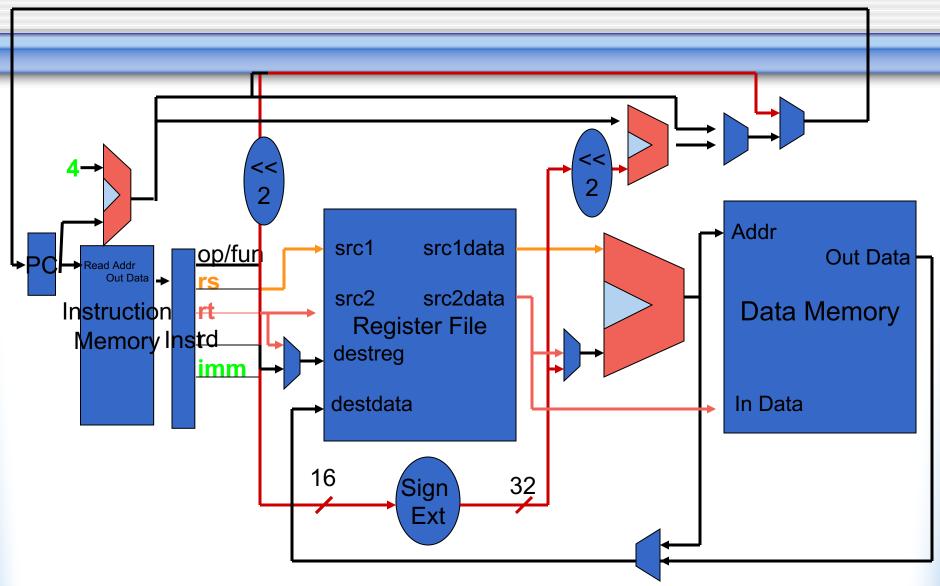

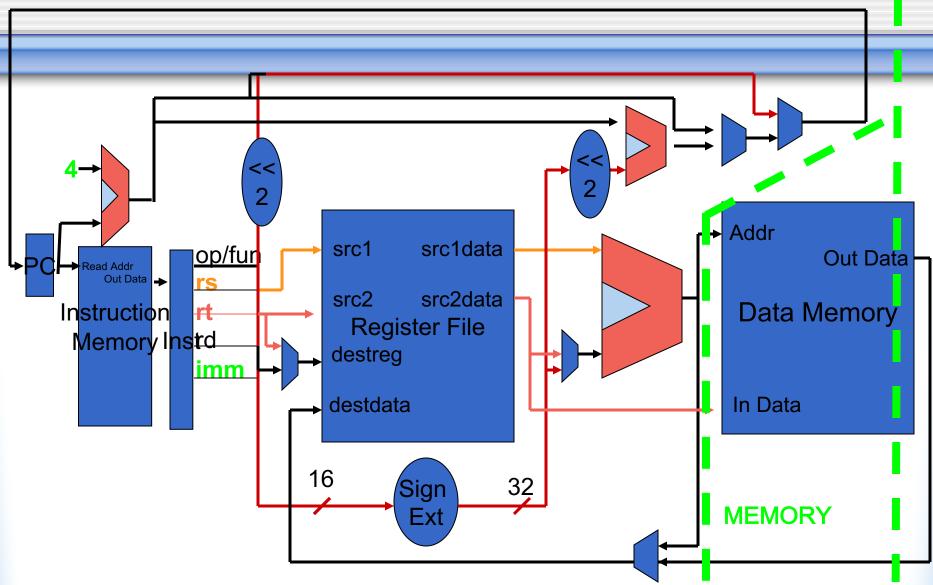

#### **The Whole Shebang**

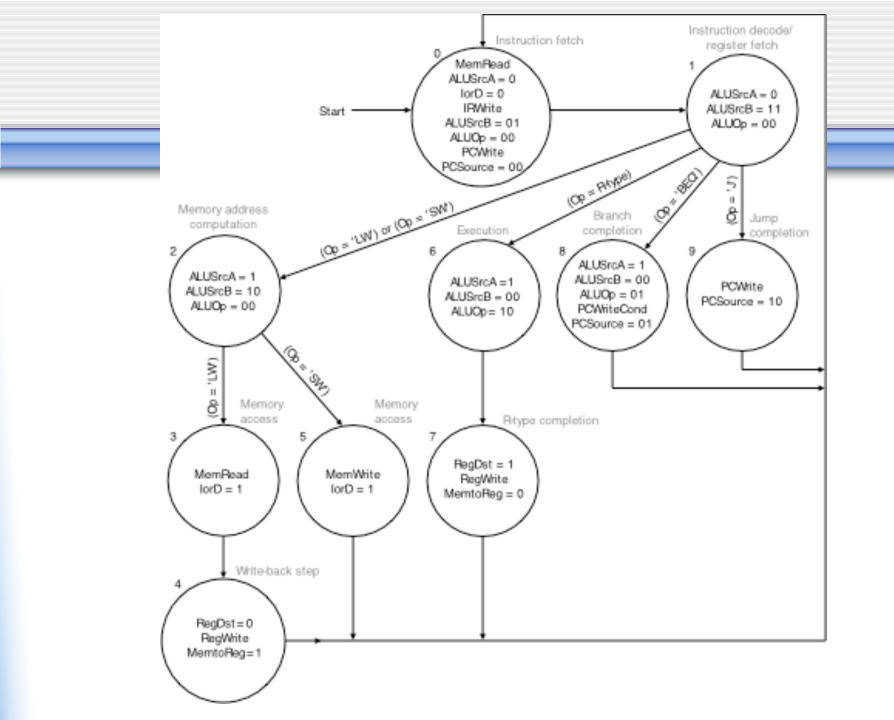

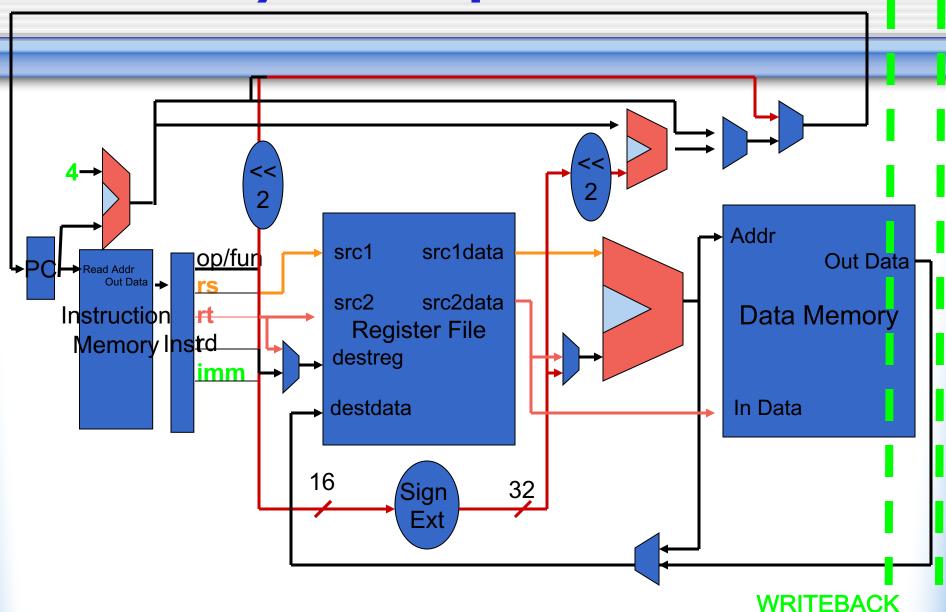

# **Control Unit**

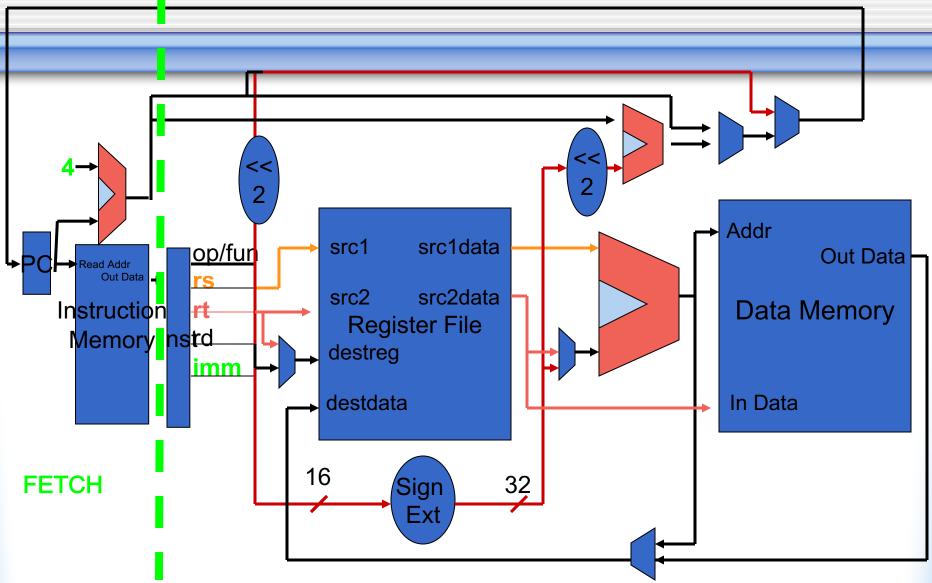

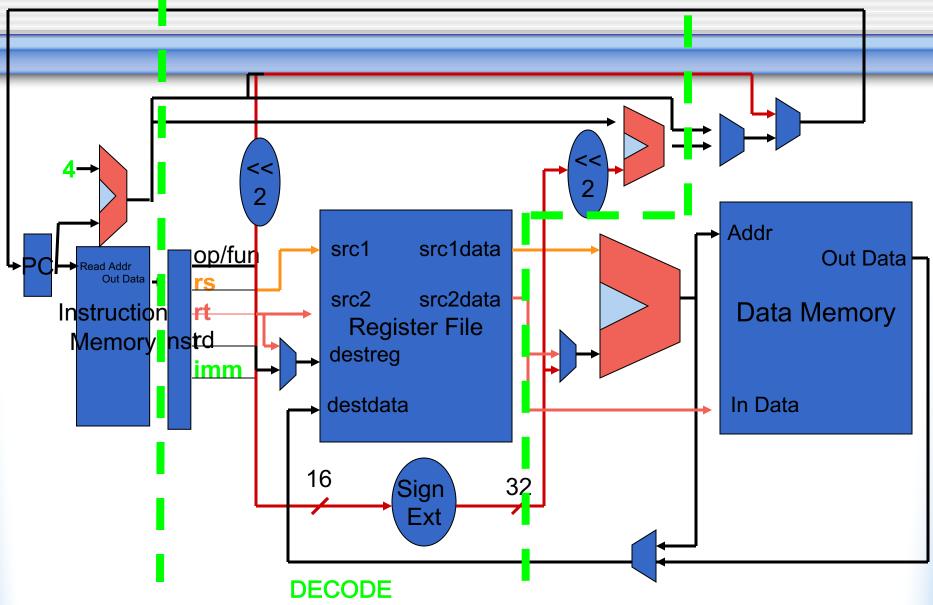

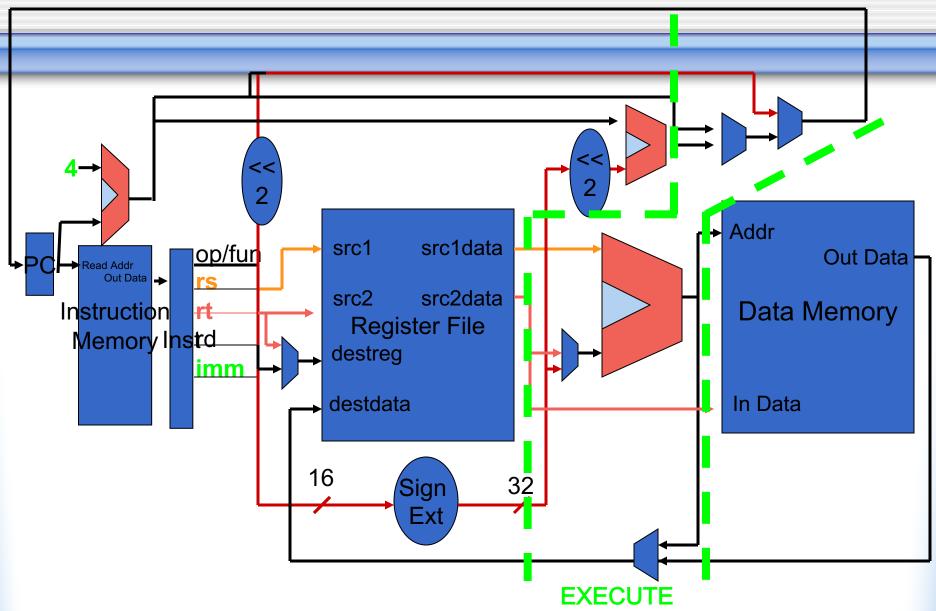

- Set of control line values cause appropriate actions to be taken at each step

- Finite state machine determines what needs to be done at each step

- Fetch

- Decode

- Execute

- Memory

- Writeback

ACTIONS DEPEND ON OPCODE

#### **Single Cycle Latency**

## **Time Diagram**

# **Cycle Time**

- Not all instructions must go through all steps

- add doesn't need to go to memory

- Single long clock cycle makes add take as long as load

- Can we change this?

- Break single instruction execution into small execution steps

## **How Many Cycles For:**

- add

- SW

- Iw

- blt

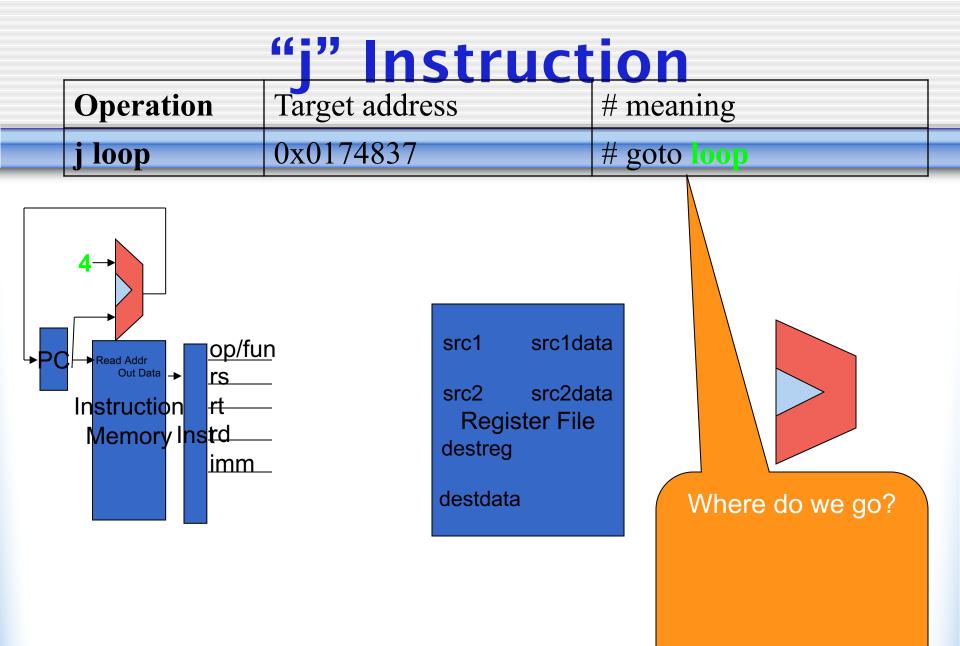

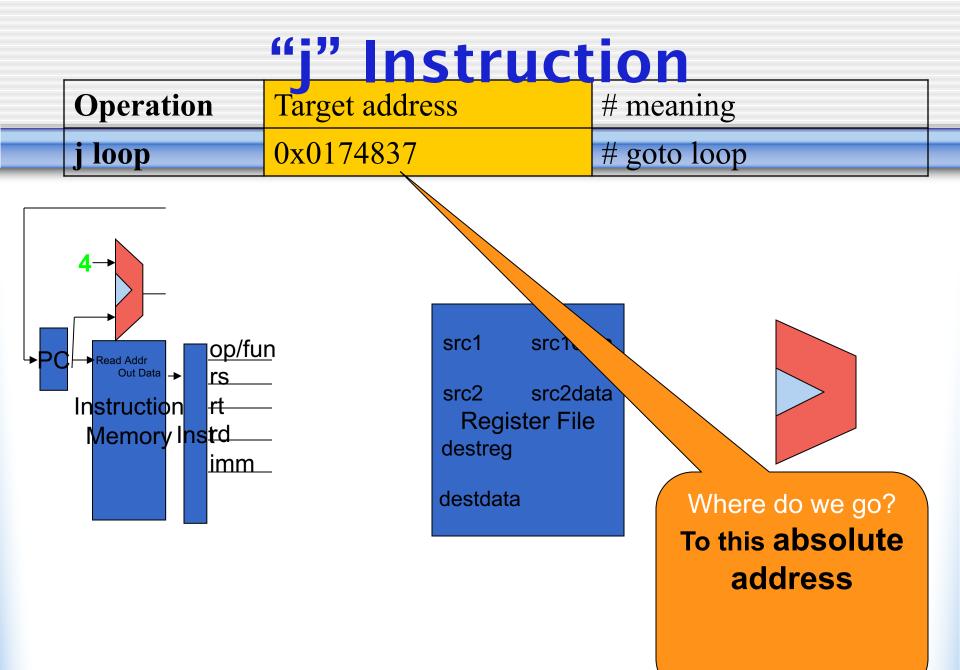

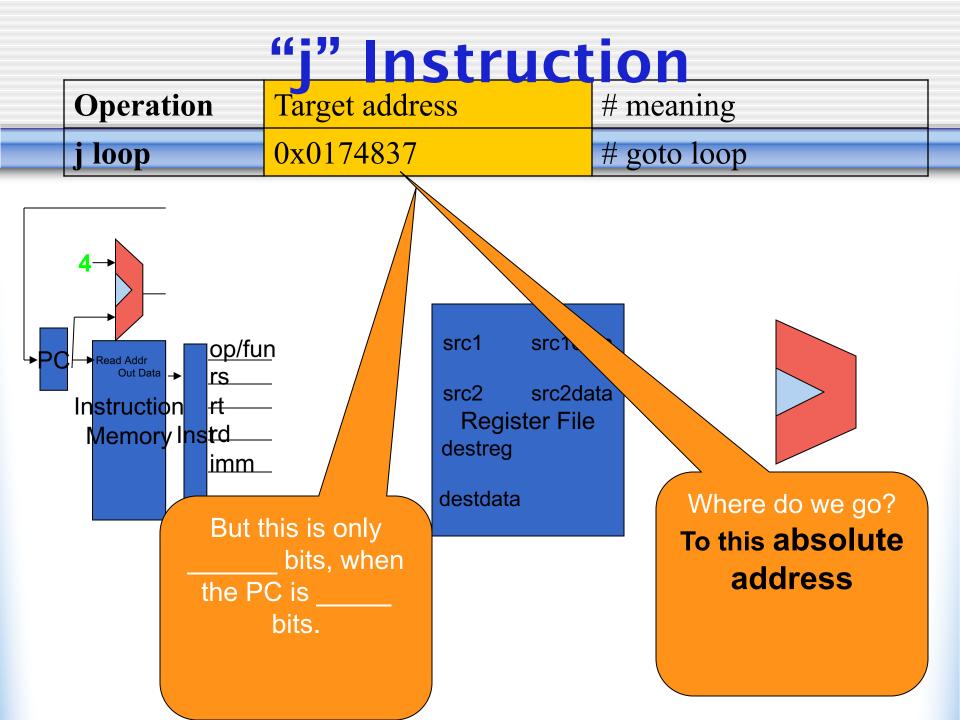

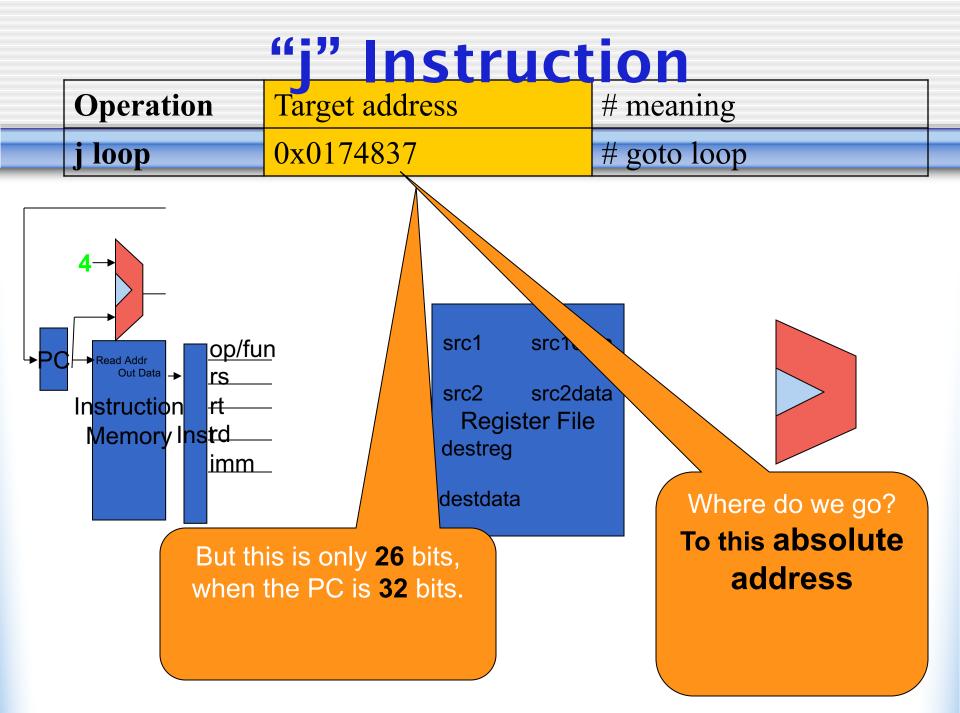

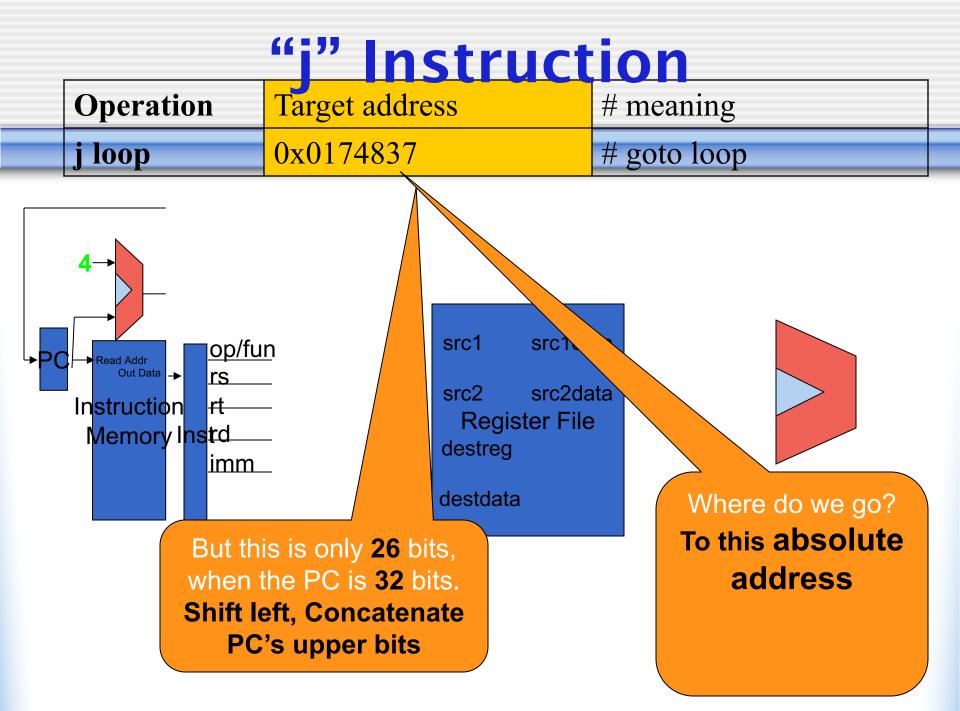

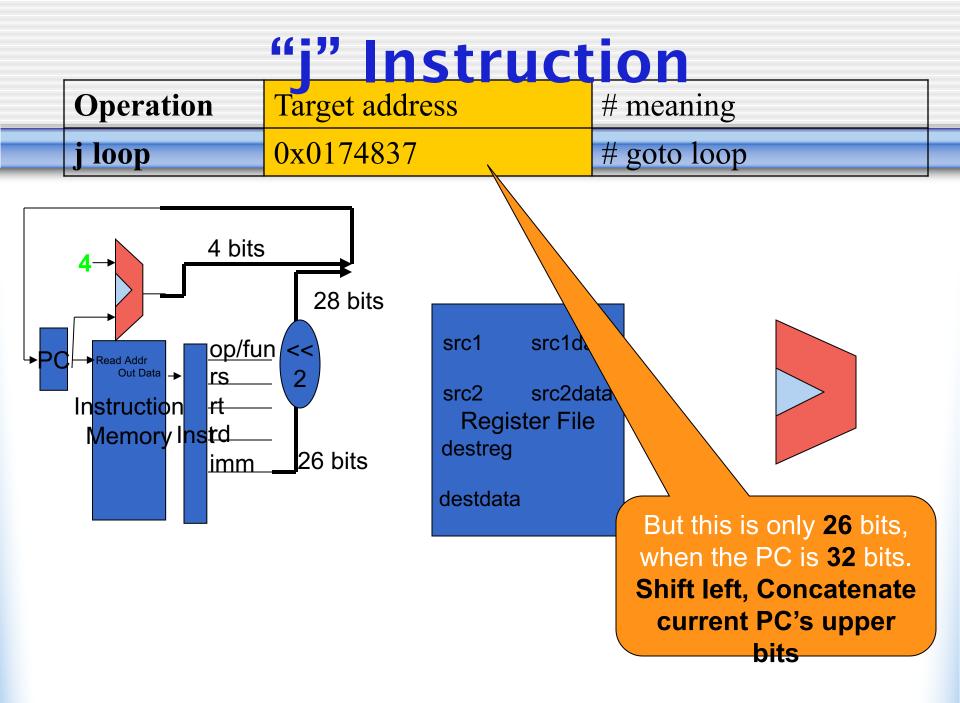

- j